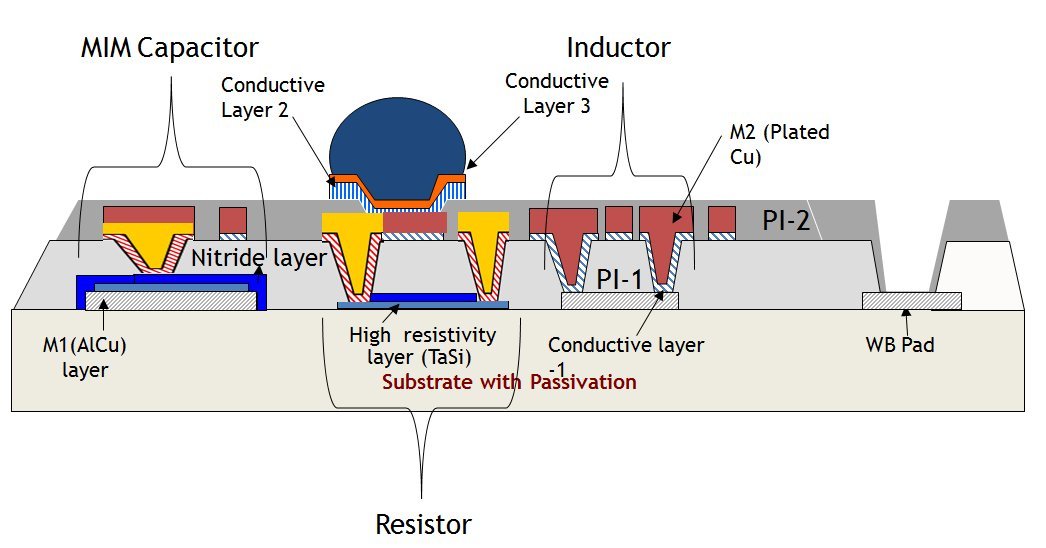

- 晶圓級封裝技術晶圓級封裝(WLP)與扇出封裝技術當今的消費者正在尋找性能強大的多功能電子設備,這些設備不僅要提供前所未有的性能和速度,還要具有小巧的體積和低廉的成本。這給半導體制造商帶來了復雜的技術和制造挑戰,他們試圖尋找新的方法,在小體積、低成本的器件中提供更出色的性能和功能。長電技術優勢長電科技在提供全方位的晶圓級技術解決方案平臺方面處于行業領先地位,提供的解決方案包括扇入型晶圓級封裝 (FIWLP)、扇出型晶圓級封裝 (FOWLP)、集成無源器件 (IPD)、硅通孔 (TSV)、包封芯片封裝 (EC

- 關鍵字:

封裝 測試 長電科技

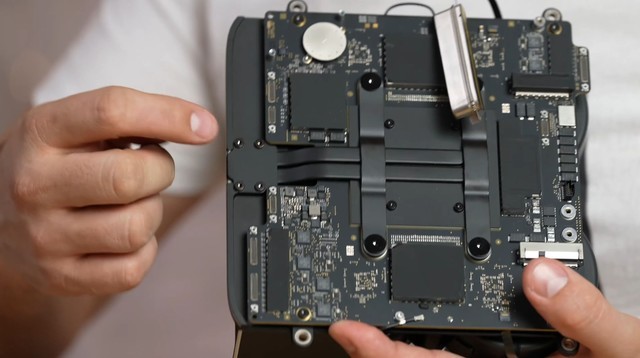

- 據外媒videocardz報道,Mac Studio的全面拆解表明,蘋果最新的M1 Ultra芯片到底有多大。此多芯片模塊包含兩個使用

UltraFusion 技術相互連接的 M1 max

芯片。需要注意的是,這款超大型封裝還包含128GB內存。不幸的是,在拆卸過程中看不到硅芯片,因為整個封裝被一個非常大的集成散熱器覆蓋。M1 Ultra具有兩個10核CPU和32核GPU。整體有1140億個晶體管。根據蘋果的基準測試,該系統應該與采用RTX 3090顯卡的高端臺式機競爭。雖然該系統確實功能強大,并

- 關鍵字:

蘋果 M1 Ultra 封裝 CPU

- 作為全球第二大的芯片代工廠,最近三星又在芯片領域做出重要一步。三星電子在其 DX 事業部的全球制造和基礎設施部門內設立了測試和封裝(TP,Test & Package)中心。

- 關鍵字:

三星 封裝 業務

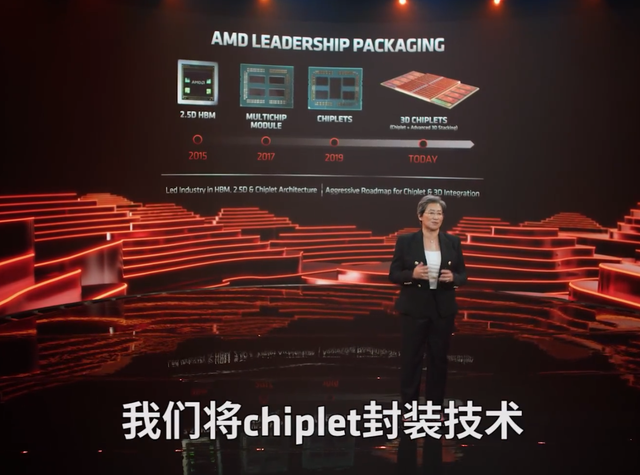

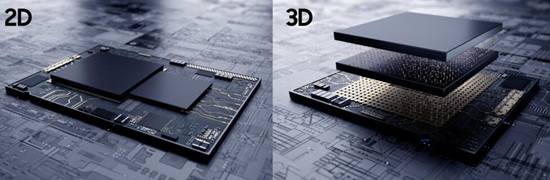

- 6 月 1 日消息 在今日召開的 2021 臺北國際電腦展(Computex 2021)上,AMD CEO 蘇姿豐發布了 3D Chiplet 架構,這項技術首先將應用于實現“3D 垂直緩存”(3D Vertical Cache),將于今年年底前準備采用該技術生產一些高端產品。蘇姿豐表示,3D Chiplet 是 AMD 與臺積電合作的成果,該架構將 chiplet 封裝技術與芯片堆疊技術相結合,設計出了銳龍 5000 系處理器原型。官方展示了該架構的原理,3D Chiplet 將一個 64MB 的 7n

- 關鍵字:

AMD chiplet 封裝

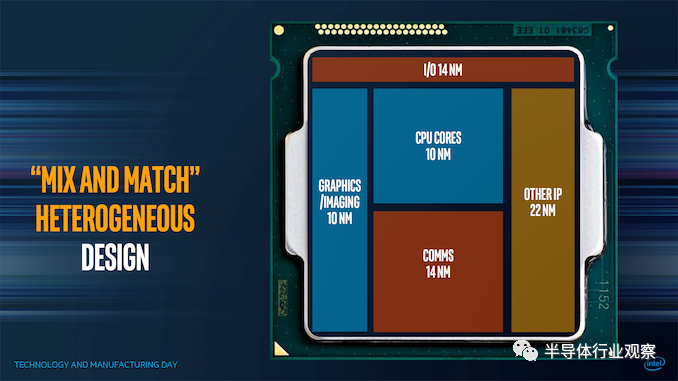

- 在英特爾2020年架構日活動即將結束的時候,英特爾花了幾分鐘時間討論它認為某些產品的未來。英特爾客戶計算部門副總裁兼首席技術官Brijesh Tripathi提出了對2024年以上未來客戶端產品前景的展望。他表示,他們將以英特爾的7+制造工藝為中心,目標是啟用“Client 2.0”,這是一種通過更優化的芯片開發策略來交付和實現沉浸式體驗的新方法。Chiplet(小芯片)并不是新事物,特別是隨著英特爾競爭對手最近發布的芯片,并且隨著我們進入更復雜的過程節點開發,小芯片時代可以使芯片上市時間更快,給定產品的

- 關鍵字:

英特爾 chiplet 封裝

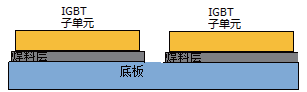

- 長期進行IGBT器件焊接封裝發現,IGBT器件封裝所用關鍵部件子單元的存放時間長短對焊接空洞影響較大,本文分別對兩批存放時間差別較大的子單元進行封裝,通過實驗對比兩批產品的空洞率,結果表明存放時間較短的子單元焊接的IGBT器件空洞率明顯偏小,從而提高了IGBT器件的可靠性。

- 關鍵字:

IGBT 焊接 封裝 空洞率 子單元 202201

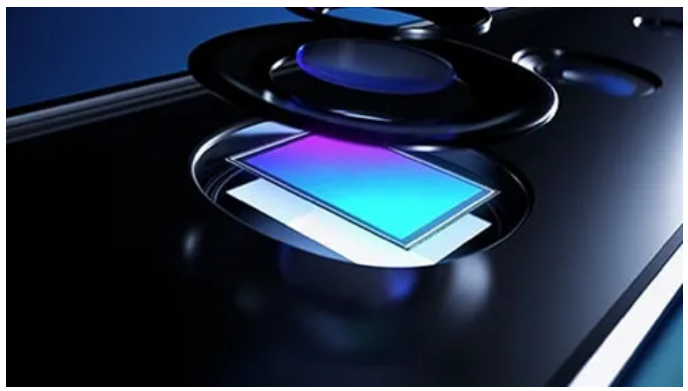

- 據國外媒體報道,三星電子計劃采用一種新的封裝技術,以降低圖像傳感器的成本。從外媒的報道來看,三星圖像傳感器計劃采用的是芯片級封裝(Chip Scale Package,CSP)技術,從明年開始采用,不過只會用于低分辨率的圖像傳感器。COB封裝技術據The Elec報道,目前三星電子的圖像傳感器采用板上芯片封裝(Chips on Board,COB) ——?COB是當前圖像傳感器最常用的封裝方法,即將圖像傳感器放置在PCB上,并通過導線連接,再將鏡頭附著在上面。然而,該過程需要一個潔凈室,因為在封

- 關鍵字:

三星 圖像傳感器 CSP 封裝

- 5G通信與新能源汽車引領的新一輪科技迭代浪潮,將全球半導體行業引入了新一輪景氣周期。面對強勁市場需求,包括封測在內的行業相關企業普遍迎來業績利好。日前,國內封測龍頭長電科技(股票代碼600584)發布了截至2021年6月30日的半年度財務報告。財報顯示,長電科技上半年實現營收人民幣138.2億元,同比增長15.4%。凈利潤為人民幣13.2億元,同比增長261.0%,創歷年上半年凈利潤新高。自2020年起,長電科技進入增長快車道,去年全年凈利潤達到13億元。進入2021年,長電科技的業績增速勢頭不減,上半年

- 關鍵字:

封裝 先進

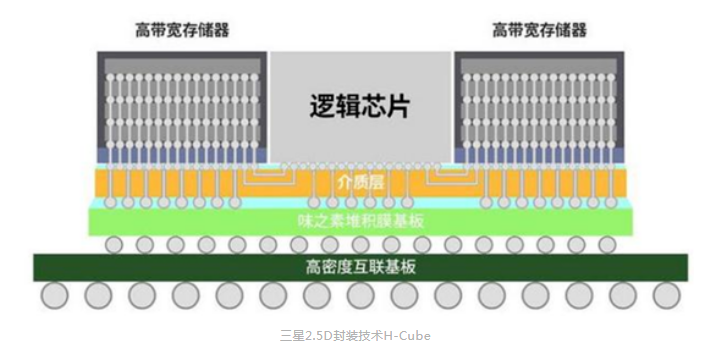

- 據國外媒體報道,本月中旬,三星展示了他們的3D芯片封裝技術,而外媒最新的報道顯示,三星已加快了這一技術的部署。外媒是援引行業觀察人士透露的消息,報道三星在加快3D芯片封裝技術的部署的。加快部署,是因為三星尋求明年開始同臺積電在先進芯片的封裝方面展開競爭。從外媒的報道來看,三星的3D芯片封裝技術名為“eXtended-Cube” ,簡稱“X-Cube”,是在本月中旬展示的,已經能用于7nm制程工藝。三星的3D芯片封裝技術,是一種利用垂直電氣連接而不是電線的封裝解決方案,允許多層超薄疊加,利用直通硅通孔技術來

- 關鍵字:

三星 3D 芯片 封裝 臺積電

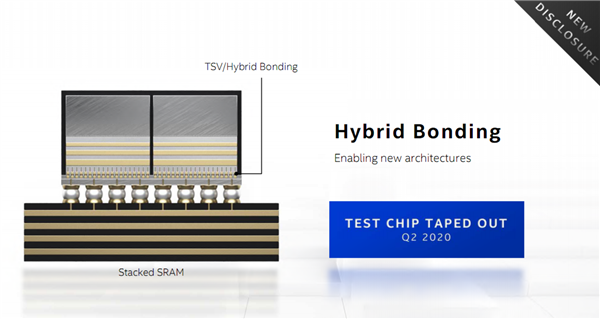

- 在Intel的六大技術支柱中,封裝技術和制程工藝并列,是基礎中的基礎,這兩年Intel也不斷展示自己的各種先進封裝技術,包括Foveros、Co-EMIB、ODI、MDIO等等。Intel又宣布了全新的“混合結合”(Hybrid Bonding),可取代當今大多數封裝技術中使用的“熱壓結合”(thermocompression bonding)。據介紹,混合結合技術能夠加速實現10微米及以下的凸點間距(Pitch),提供更高的互連密度、更小更簡單的電路、更大的帶寬、更低的電容、更低的功耗(每比特不到0.0

- 關鍵字:

Intel 封裝 凸點密度

- 據臺灣媒體報道,三星電子成功研發3D晶圓封裝技術“X-Cube”,稱這種垂直堆疊的封裝方法,可用于7納米制程,能提高該公司晶圓代工能力。圖片來自三星電子官方三星的3D IC封裝技術X-Cube,采用硅穿孔科技(through-silicon Via、簡稱TSV),能讓速度和能源效益大幅提升,以協助解決次世代應用嚴苛的表現需求,如5G、人工智能(AI)、高效能運算、行動和穿戴設備等。三星晶圓代工市場策略的資深副總裁Moonsoo Kang表示,三星的新3D整合技術,確保TSV在先進的極紫外光(EUV)制程節

- 關鍵字:

三星 3D 晶圓 封裝

- 摘要傳感器半導體技術的開發成果日益成為提高傳感器集成度的一個典型途徑,在很多情況下,為特殊用途的MEMS(微機電系統)類傳感器提高集成度的奠定了堅實的基礎。本文介紹一個MEMS光熱傳感器的封裝結構以及系統級封裝(SIP)的組裝細節,涉及一個基于半導體技術的紅外傳感器結構。傳感器封裝以及其與傳感器芯片的物理交互作用,是影響系統整體性能的主要因素之一,本文將重點介紹這些物理要素。本文探討的封裝結構是一個腔體柵格陣列(LGA)。所涉及材料的結構特性和物理特性必須與傳感器的光學信號處理和內置專用集成電路(ASIC

- 關鍵字:

紅外傳感器 封裝 光窗 紅外濾光片 MEMS

- 封裝是半導體生產流程中的重要一環,也是半導體行業中,中國與全球差距最小的一環。然而,新冠肺炎疫情的突襲,讓中國封裝產業受到了一些影響。但是,隨著國內數字化、智能化浪潮的不斷推進,中國的封裝產業增加了更多沖破疫情陰霾、拓展原有優勢取得進一步發展的機會。

- 關鍵字:

封裝 半導體 5G新基建

- 盛美半導體設備公司,作為國際領先的半導體和晶圓級封裝設備供應商,近日發布公司新產品:適用于晶圓級先進封裝應用(Wafer Level Advance Package)的無應力拋光(Stree-Free-Polish)解決方案。先進封裝級無應力拋光(Ultra SFP ap)設計用于解決先進封裝中,硅通孔(TSV)和扇出(FOWLP)應用金屬平坦化工藝中表層銅層過厚引起晶圓翹曲的問題。

- 關鍵字:

盛美半導體 晶圓 封裝

- 全球領先的高科技設備制造商Manz亞智科技,交付大板級扇出型封裝解決方案于廣東佛智芯微電子技術研究有限公司(簡稱佛智芯),推進國內首個大板級扇出型封裝示范線建設,是佛智芯成立工藝開發中心至關重要的一個環節,同時也為板級扇出型封裝裝備奠定了驗證基礎,從而推進整個扇出型封裝(FOPLP)行業的產業化發展。5G、云端、人工智能等技術的深入發展,使其廣泛應用于移動裝置、車載、醫療等行業,并已成為全球科技巨擘下一階段的重點發展方向。而在此過程中,體積小、運算及效能更強大的芯片成為新的發展趨勢和市場需求,不僅如此,芯

- 關鍵字:

封裝 FOPLP

封裝介紹

程序 封裝 (encapsulation)

隱藏對象的屬性和實現細節,僅對外公開接口,控制在程序中屬性的讀和修改的訪問級別.

封裝 (encapsulation)

封裝就是將抽象得到的數據和行為(或功能)相結合,形成一個有機的整體,也就是將數據與操作數據的源代碼進行有機的結合,形成“類”,其中數據和函數都是類的成員。

封裝的目的是增強安全性和簡化編程,使用者不必了解具體的 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473