SiC MOSFET 界面陷阱檢測升級:Force-I QSCV 方法詳解

電容-電壓 (C-V) 測量廣泛用于半導體材料和器件表征,可提取氧化物電荷、界面陷阱、摻雜分布、平帶電壓等關鍵參數。傳統基于 SMU 施加電壓并測量電流的準靜態方法適用于硅 MOS,但在 SiC MOS 器件上因電容更大易導致結果不穩定。為解決這一問題,Keithley 4200A-SCS 引入 Force-I QSCV 技術,通過施加電流并測量電壓與時間來推導電容,獲得更穩定可靠的數據。

Force-I QSCV 技術在 SiC 功率 MOS 器件上體現出多項優勢。比如僅需 1 臺帶前置放大器的 SMU 即可完成測試,而傳統方法通常需要兩臺;以電流驅動代替電壓掃描,既提高速度又能在器件端維持恒定直流,建立真正的穩態 C-V 條件,避免電壓階躍帶來的動態誤差;同時采用電壓測量方式,有效規避低輸出阻抗儀器在推導電容時常見的穩定性問題。系統支持開路校準和泄漏校準,確保測量精度;其結果與吉時利 595 準靜態 C-V 表高度一致,并可利用正向、反向掃描曲線提取界面態密度 DIT;此外,該技術對大于 20 pF 的較大電容同樣適用。

本文介紹了Force-I QSCV技術, 解釋了如何在Clarius軟件中使用這些測試,將該技術與其他方法進行了比較,驗證了 Force-I QSCV 在測量速度、穩定性、精度及設備需求方面的顯著優勢。

使用三步法的Force-I QSCV技術

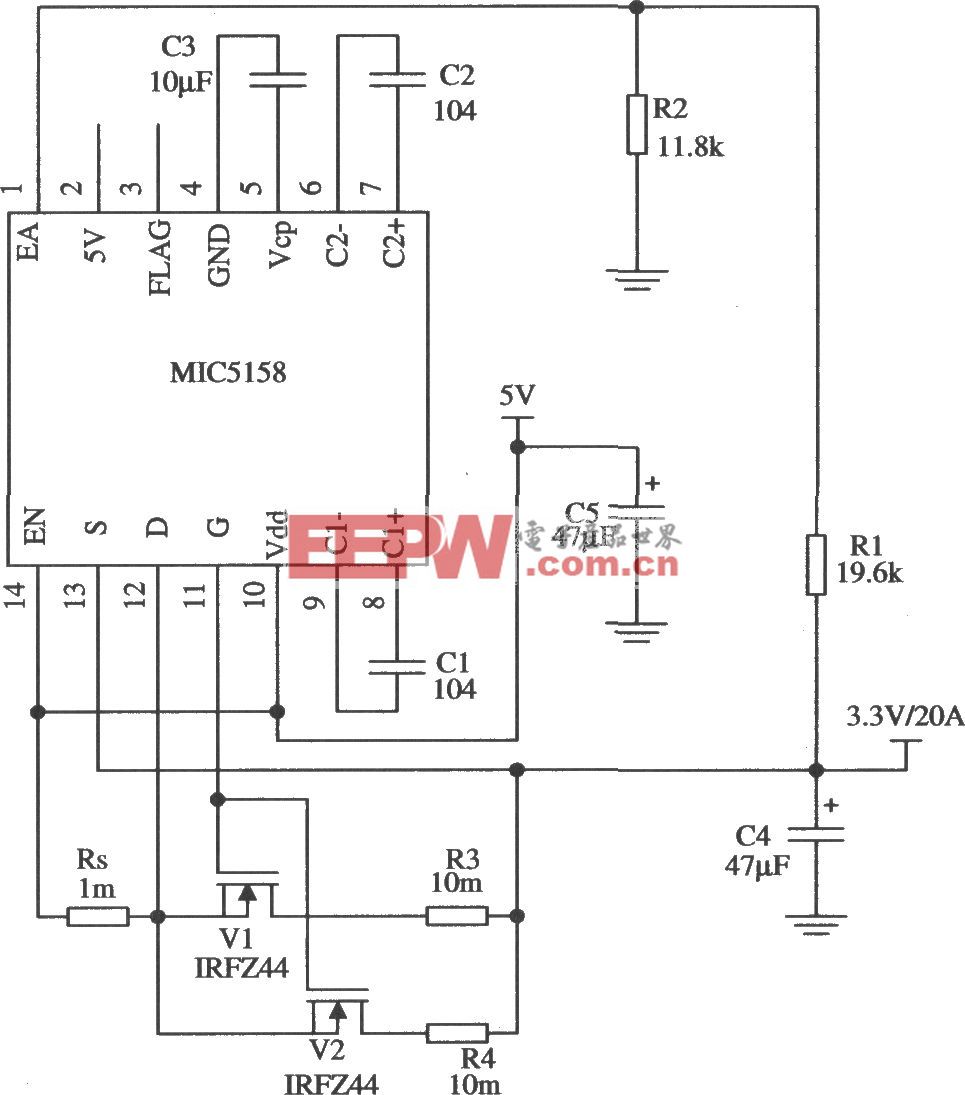

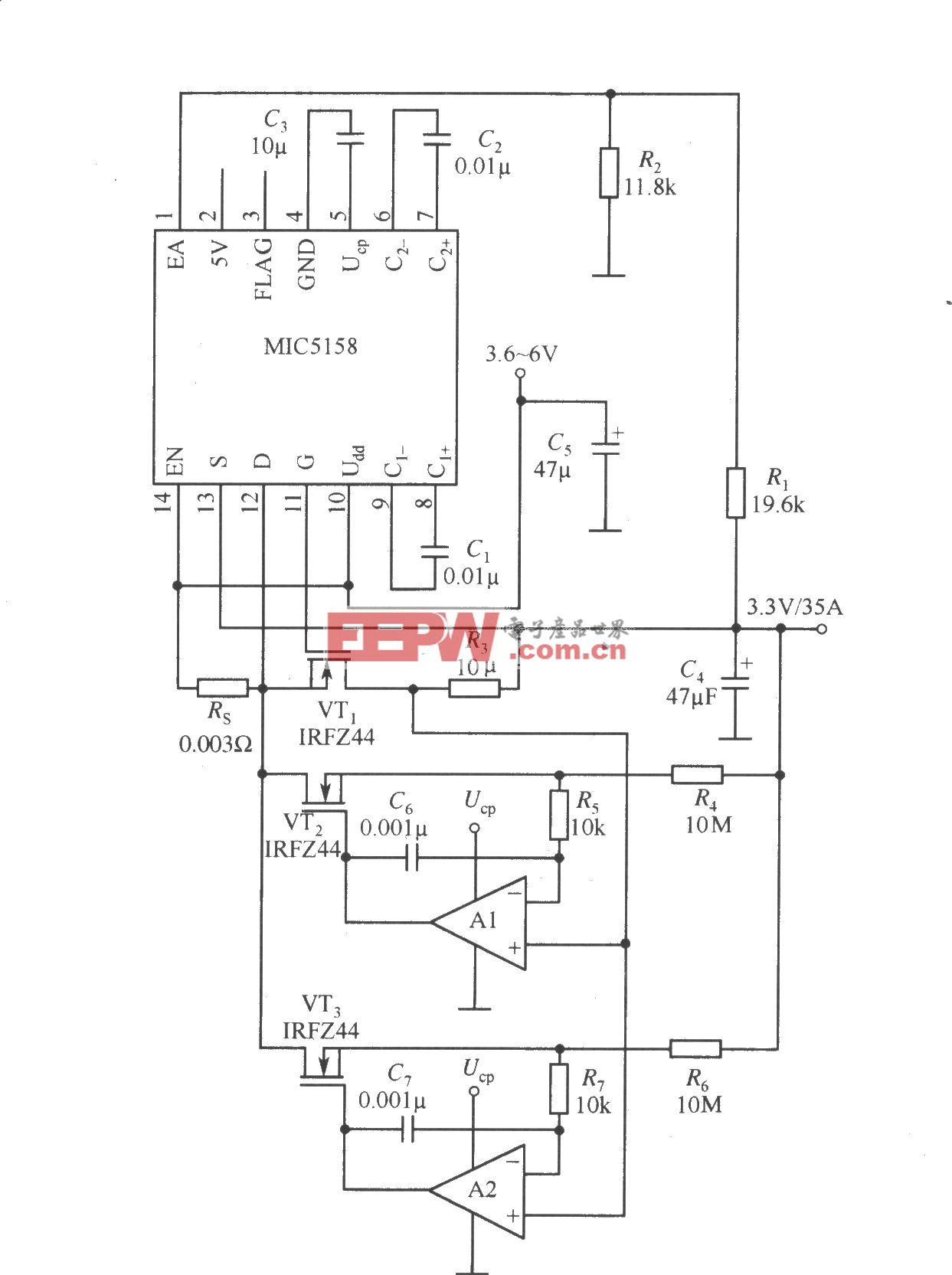

Force-I QSCV技術使用一個帶前置放大器的SMU來推導SiC MOSFET或MOS電容的準靜態C-V特性。SMU是一種能夠施加和測量電流和電壓的儀器。如圖1所示,SMU的Force HI端子連接到功率MOSFET的柵極,SMU的Force LO端子連接到短接在一起的漏極和源極端子。

圖1. 功率MOSFET在SMU的HI和LO端子之間的連接圖

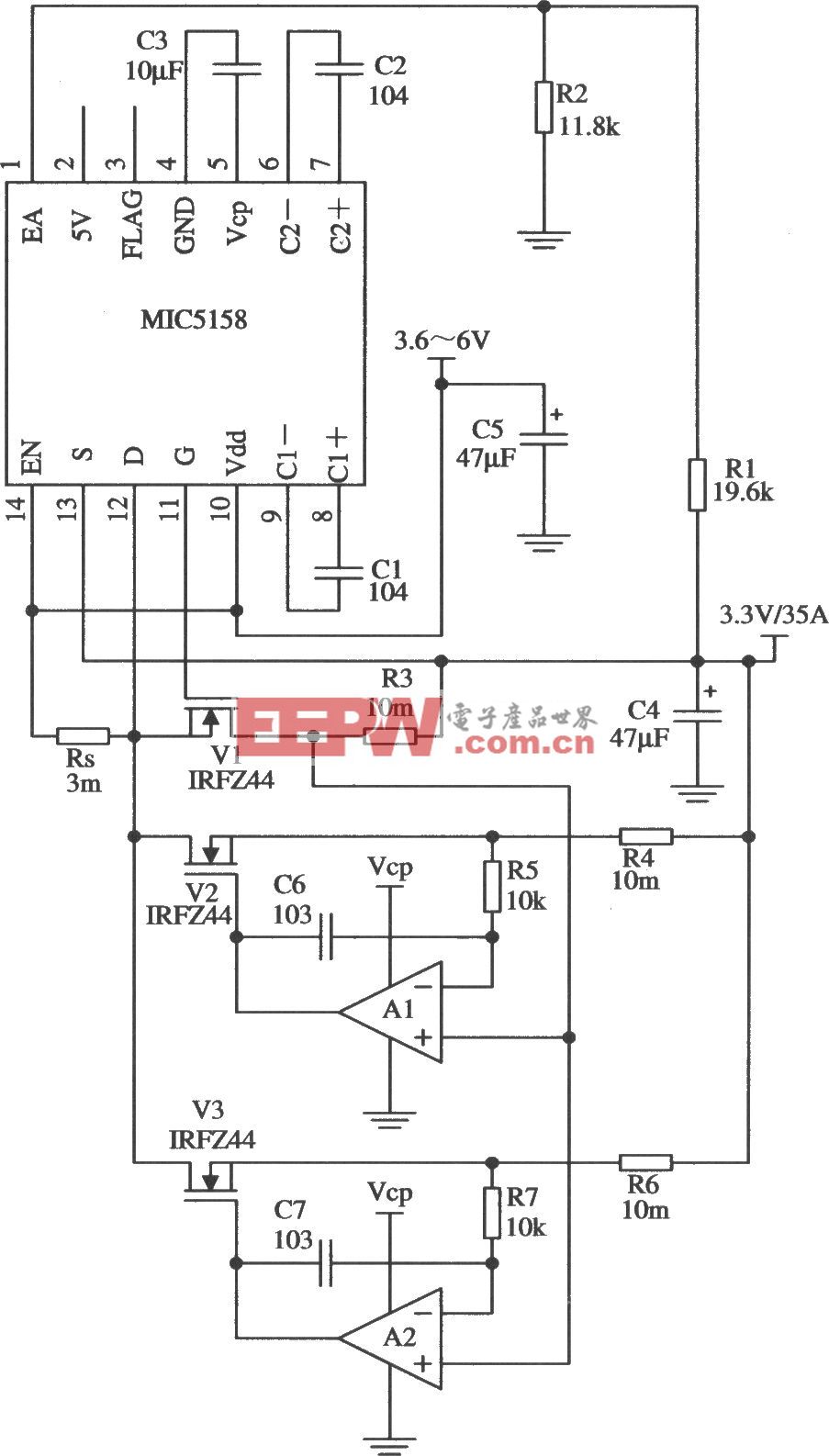

施加電流準靜態C-V方法通過施加正負電流并測量電壓隨時間的變化,使用三步法推導正向和反向C-V曲線。恒定電流可精確控制提供給器件的總電荷(Q= ∑ I×dt)。與可能導致測量設備動態變化的電壓步進不同,使用恒定電流可使儀器達到穩態條件。三步法的電壓和電流時序圖如圖2所示。

圖2. Force-I QSCV測試的電流和電壓時序圖

使用Clarius軟件進行Force-I QSCV測試

使用Force-I QSCV方法的測試位于測試庫和項目庫中,可以在 “選擇” 視圖中通過搜索 “force-I QSCV” 或“qscv”找到。 在測試庫中找到測試后,可以選擇它們并將其添加到項目樹中。測試庫包括適用于 SiCMOSFET(sic-mosfet-force-i-qscv)和SiC MOS電容 (sic-moscap-force-i-qscv) 的測試。這些特定測試可以用于其他器件,也可以通過向項目樹添加自定義測試(UTM)并使用QSCVulib用戶庫中的force_current_CV用戶模塊來創建新測試。表1列出了所有輸入參數及其描述和注釋。以下描述了Force-I QSCV測試的輸入參數、輸出參數以及結果分析。

表1 施加電流的QSCV測試的輸入參數

Force-I QSCV測試的輸入參數顯示在Clarius的“配置”視圖中,如圖3所示。用戶設置最大和最小測試電壓、輸出電流和時序參數。開路補償和泄漏校準為可選功能,也可以在 “配置” 視圖中應用。

圖3. 在Clarius中配置Force-I QSCV測試的視圖

對于SiC MOSFET,施加電流通常在數百皮安到納安范圍內。測試電流的大小應約為要測量的最大電容大小的三分之一。例如,如果最大電容為2.4×10-9F,則測試電流應約為800×10-12A。測試電流過低或過高都可能導致錯誤結果。

PLC時序設置調整測量的積分時間,可在0.01到10的范圍內設置。然而,最好使用1到6之間的PLC值。此設置會影響測量時間以及電壓步長,電壓步長是讀數之間的電壓差。理想情況下,步長應在50mV到100mV之間。電壓步長可以使用公式編輯器中的DELTA函數計算。增加PLC延長了測量時間,但會改善噪聲讀數。

漏電校準和校準延遲:默認情況下,漏電校準處于禁用狀態。如果啟用,將在每個電壓點測量并校準漏電。漏電校準分三步完成:

1) 使用恒定電流推導C-V正向和反向掃描。

2) 在第一步返回的每個電壓點測量正向和反向泄漏電流。

3) 最后,使用測量的校準漏電返回電容值 (CrCorr和CfCorr)。漏電在固定電流范圍內測量,并可以實時繪制。漏電校準使用以下校準電容公式:

![]()

校準后的反向電容CrCorr與Vr相對繪制,校準后的正向電容CfCorr與Vf相對繪制。如果校準后的電容看起來有噪聲,增加施加電流并重復測試。電流 ( 位移電流 ) 必須高于泄漏電流,否則無法校準泄漏電流。位移電流定義為:I = C*(dV/dt)。

圖4和圖5顯示了有和沒有漏電校準的QSCV曲線示例。測試運行了一次,生成了未校準和校準后的數據。圖4顯示了一個有泄漏的SiC功率MOSFET的正向 (Cf) 和反向 (Cr) C-V曲線。

圖4. 漏電碳化硅MOSFET的正向和反向準靜態C-V曲線;圖5. 碳化硅MOSFET的校準前向和反向C-V曲線

電容偏移和開路補償均用于校準測試電路中的電容 ( 如電纜、測試夾具或探頭 ) 引起的偏移。這兩個選項顯示在測試的 “配置” 視圖中,如圖6所示。

圖6. 偏置校準和打開補償窗口

默認情況下,電容偏移設置為0F,但用戶可以輸入一個電容值,該值將從正向和反向電容讀數中減去。開路補償可以設置為“無”、“測量補償”或“應用補償”。如果選擇 “無”,則不會將任何開路補償測量寫入文件或應用。

如果啟用 “測量補償”,則在開路情況下(器件從測試夾具中移除或探針抬起)運行測試。至少約有3-5pF的最小電容能被校準,否則會發生錯誤 (-35),這意味著SMU處于限制狀態。通常,開路的施加電流將在1×10-13A或更小范圍內,以避免測試進入電壓限制狀態。由于測試電流非常小,測試將需要幾分鐘才能執行完成并獲取偏移電容。獲取的開路數據的平均值存儲在文件中,并將在使用 “應用補償數據” 時從讀數中減去。減去的電容值在工作表中顯示為Copen。

一旦使用 “測量補償” 運行測試,將被測器件連接到測試電路中,并再次運行測試,啟用 “應用補償”。確保將施加電流調整到適合器件的水平。當第二次執行測試時,從 “測量補償” 獲取的平均電容 (Copen) 將從后續讀數中減去。

分析結果

使用適當的輸入設置配置測試后,可以通過選擇“運行”來執行測試。運行測試時,將向被測器件施加恒定電流,如步驟1、2和3所述,對器件進行充電并生成反向和正向C-V曲線。

“分析” 視圖圖形將顯示測量結果。電壓隨時間的測量值將實時顯示在左側圖形中,電壓測量完成后,正向和反向C-V掃描將顯示在右側圖形中。

數據被拆分為反向和正向C-V掃描,以準確表示測量結果。對于反向掃描,輸出反向電壓 (Vr)、反向掃描時間(timeR) 和反向電容 (Cr)。在正向掃描中,輸出反向電壓(Vf)、正向掃描時間 (timeF) 和電容 (Cf)。

圖7顯示了使用sic-mosfet-force-i-qscv庫測試對市面上可買到的某個SiC功率MOSFET進行測試的 Clarius圖形視圖結果。對于此測試,使用8×10-10A 的測試電流和4的PLC作為測試設置。使用4的PLC 時,電壓步長接近80mV。請注意,在正向和反向掃描中,曲線存在電壓偏移和峰值。在曲線右側的正向掃描和左側的反向掃描中觀察到峰值。這些偏移通常因為內部器件電荷的移動。

圖7. 碳化硅MOSFET的電壓與時間(左)和反向與正向C-V曲線(右)

圖8. SiC MOSFET上的正向和反向準靜態C-V掃描。

圖8顯示了另一個市售SiC MOSFET的準靜態C-V曲線。在這種情況下,正向 ( 紅色 ) 曲線具有反向掃描中未出現的類似“可動離子” 的峰值。對于此測試,輸入參數設置如下:測試電流5×10-10A,8PLC,最大電壓10V,最小電壓-12V,限壓20V。

除了在圖形工具中查看數據外,多個參數還會返回到分析視圖的表格中。以下表格列出了這些輸出參數,并按表格中顯示的順序分為以下類別:主要輸出參數、反向輸出參數、正向輸出參數、用于DIT提取的參數和雜項參數。

表2 主要的輸出參數

表3 反向輸出參數

表4 正向輸出參數

表5 DIT提取用到的參數

表6 其他輸出參數

Force-I QSCV與高頻C-V的比較

優化Force-I QSCV有如下幾種方法:

最小電容:可以測量的最小電容在 10-20pF 之間。此方法推薦電容通常在 nF 范圍內的 SiC 器件。

對器件進行靜電屏蔽:由于此方法可測試非常小的電荷,因此對被測器件進行靜電屏蔽以避免噪聲非常重要。

電壓步長:為獲得最佳結果,電壓步長應在 50-100mV之間。可以通過更改 PLC 來調整電壓步長。電壓步長可以用測量的 “電壓” 通過公式編輯器中的 DELTA 函數來測量。

施加電流:選擇合適的電流可能需要進行一些試驗。電流過低會導致測試時間長。電流過高會導致測試達到限壓狀態。

開路補償:在大多數測量SiC器件QSCV的情況下,開路補償可能不需要,因為電纜和測試夾具電容(數十皮法)通常比被測器件電容(納法)小得多。

圖10顯示了在封裝的SiC MOSFET上使用兩種方法獲取的圖形。注意,Force-I QSCV曲線比595數據的噪聲更小,但總體而言,曲線相關性很好。

使用Force-I QSCV方法和高頻交流測量(使用4215-CVU電容電壓單元)獲取的C-V曲線進行比較。結果如圖11所示。CVU數據(綠色曲線)包含了來自595和Force-I QSCV方法的正向和反向準靜態曲線。高頻CVU數據在曲線中未顯示任何 “峰值”。

圖11. 封裝的碳化硅MOSFET的高頻和準靜態C-V掃描

結論

Force-I QSCV技術能夠在碳化硅MOS設備上實現準靜態C-V測量。該方法通過正向和反向掃描獲取兩組數據,以及通過施加正負電流獲得的電壓――時間數據。已知總電荷后,此方法可以提取半導體界面處的電容和電荷,正向和反向掃描的差分分析能夠直接提取界面陷阱密度 (DIT)。

評論