用戶可定制的處理器

移動電話領域中的Viterbi解碼的例子可以很好地說明可擴展處理器可以替代RTL硬邏輯。

GSM標準利用Viterbi解碼將信息從包含噪聲的信道中提取出來。解碼過程中會用到包括8次邏輯計算(4次加法、2次比較、2次選擇)的蝶形運算,從接收到的數(shù)據(jù)流中每解碼一個符號需要8次蝶形運算。如果采用通用RISC處理器,需要50~80個指令周期完成一次Viterbi蝶形運算,即使在TI高端的超長指令字DSP 320C64xx上,也需要1.75個周期。本文引用地址:http://www.czjhyjcfj.com/article/152554.htm

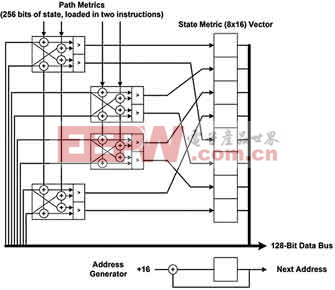

圖3 Viterbi蝶形算法硬件模塊

利用TIE語言,設計者可以為Xtensa處理器增加一條專門完成Viterbi蝶形運算的指令,使用處理器的128位寬I/O總線一次取8個符號數(shù)據(jù),如圖3所示為處理器添加運算單元和地址產生邏輯,這樣完成一次Viterbi蝶形運算只需要0.16個周期。在未擴展的Xtensa處理器上執(zhí)行Viterbi蝶形運算需要42個周期,也就是說,通過增加蝶形運算的專用硬件(大約11000門電路),就獲得了250倍的性能提升。

結論

如今,軟件模塊硬邏輯化的現(xiàn)象非常普遍。在開發(fā)協(xié)議標準的早期,通常采用基于處理器的實現(xiàn)方法,一些常見的標準,如視頻領域的MPEG2算法,3G通信領域的W-CDMA算法、安全加密領域的SSL和triple-DES算法,都是由處理器實現(xiàn)逐漸過渡到RTL硬邏輯實現(xiàn)。但是這種過渡正在被軟硬件實現(xiàn)方法間巨大的性能與設計難度差別所限制。可配置與可擴展處理器的出現(xiàn)帶來了一種新的設計方法,既可以方便快速的進行芯片開發(fā),靈活適應新的協(xié)議標準,又具有足夠小的芯片面積和功耗,從而可以進行大規(guī)模的生產。

評論