基于事件驅(qū)動的新型處理器的研究與應(yīng)用

摘要:針對現(xiàn)代電子設(shè)計低成本、高效率、高靈活性的特點,研究了一種新型的處理器:事件驅(qū)動多核心處理器。通過對這種處理器基本構(gòu)架的研究,以及采用新型處理器與采用傳統(tǒng)控制器設(shè)計差異的對比,分析出該處理器具有性能高、實時性強、易編程等優(yōu)點。最后,提出了一種新的設(shè)計方法:硬件設(shè)計軟件化,給眾多電子系統(tǒng)設(shè)計提供新的思路和參考。

本文引用地址:http://www.czjhyjcfj.com/article/149028.htm關(guān)鍵詞:XMOS;事件驅(qū)動多核心處理器;硬件線程;硬件設(shè)計軟件化

0 引言

英國的XMOS Semiconductor公司推出了一種全新的控制器件:事件驅(qū)動多核心處理器(以后簡稱XCore處理器)。憑借一種叫作軟件化芯片(Software Defined Silicon)的新技術(shù),XMOS提出了一種革命性的電子設(shè)計方法:硬件設(shè)計軟件化。通過軟件設(shè)計,可以使用XCore處理器實現(xiàn)以前需要通過FPGA,ASIC實現(xiàn)的硬件性能。這種新的處理器集RISC CPU的效率、DSP的性能和FPGA的靈活性于一體。

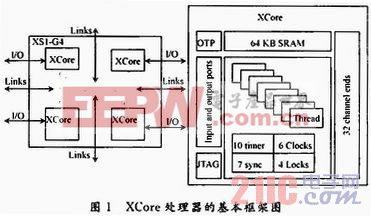

1 XCore處理器的基本構(gòu)架

圖1為XCore處理器的基本框架圖。如圖所示,每個處理器(以XS1-G4為例)有4個內(nèi)核(XCore),XCore之間通過一種稱之為X-link的技術(shù)連接,可以實現(xiàn)XCore之間的數(shù)據(jù)通信。XCore內(nèi)部有豐富的硬件資源:8 KB的OTP ROM,64 KB的RAM,10個計算器,6個時鐘模塊,7個同步單元和4個硬件鎖。除此之外,XCore最特別的是具有8個硬件線程和32個通道端(Channel Ends)以及1個事件驅(qū)動管理器。每個硬件線程具有獨立的專有寄存器組,同時可以訪問所在核內(nèi)的共享硬件資源。

通道(Channel)是線程之間通信的主要方式,一個通道可以連接幾個通道端。這樣,使用各個通道端的硬件線程就可以相互通信了。通道可以在不同的Xcore之間建立,依托強大的X-link功能,甚至不同處理器之間的線程也可以通過通道進行通信。

2 XCore處理器特點

2.1 硬件多線程技術(shù)

硬件多線程技術(shù)是XCore處理器能夠硬件設(shè)計軟件化的關(guān)鍵。有別于傳統(tǒng)的操作系統(tǒng)實現(xiàn)的多線程,硬件多線程是通過特有的硬件單元來調(diào)度。每個硬件線程的時間片精確到1個時鐘周期(對應(yīng)于處理器工作在400 MHz主頻的情況下,就是2.5 ns)。傳統(tǒng)的操作系統(tǒng)分配給線程的時間片都是在ms級。線程調(diào)度的實時性保證了多個硬件線程可以組成高性能的處理流水線。每個Xcore擁有8個硬件線程,如果這個8個線程全部運行,在400 MHz的CPU主頻的情況下,理論上可以組成一條8級的主頻為50 MHz的流水線;如果處理器內(nèi)的4個XCore全部運行,則可以組成4條這樣的并行流水線。這足以完成大部分中低性能的FPGA實現(xiàn)的功能。

2.2 多功能智能IO模塊

多功能智能IO模塊是XCore處理器的另一大特色,該模塊可以對IO數(shù)據(jù)進行處理,然后再將數(shù)據(jù)緩存后送CPU內(nèi)核處理,這樣,可以減輕IO操作對CPU內(nèi)核的負(fù)擔(dān)。使得流水線設(shè)計瓶頸可以緩解。設(shè)計者可以適當(dāng)延長處理流水線每一級的長度,使得軟件設(shè)計更加靈活,功能更加強大。

多功能智能IO模塊具有以下幾個功能:端口寬度可編程;帶時鐘、片選的IO接口;可編程時序IO接口;序列化IO接口;可編程FIFO緩存接口;可編程條件IO接口。靈活運用這些功能,可以輕易的實現(xiàn)MII,ULPI等高速總線接口。

2.3 事件驅(qū)動運算

相對于操作系統(tǒng)管理下的軟件線程,XCore處理器的硬件線程具有同樣的靈活性。每個硬件線程可以被阻塞,當(dāng)硬件線程被阻塞時處于睡眠狀態(tài),它所占用的時鐘周期可以釋放給其他的硬件線程。舉個例子,如果某個XCore以400MHz的工作頻率運行8個線程,那么每個硬件線程的實際工作頻率是50 MHz。當(dāng)其中4個線程被阻塞時,剩下的4個硬件線程的工作頻率就能夠提升到100MHz。當(dāng)線程被阻塞時,需要等待指定的事件將它喚醒,這些事件可以由定時器、智能IO模塊和線程之間通信的通道產(chǎn)生。基于事件驅(qū)動運算的機制,可以極大地減少XCore處理器的功耗并顯著地提升XCore處理器的效能。

3 實例介紹

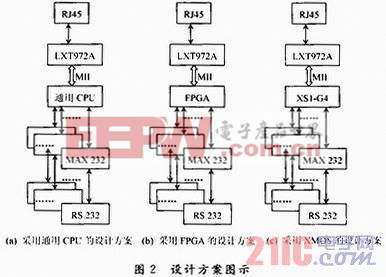

串口服務(wù)器是在工業(yè)控制領(lǐng)域經(jīng)常用到的一類設(shè)備,其作用是實現(xiàn)UART與以太網(wǎng)之間的協(xié)議轉(zhuǎn)換,下面給出了3個不同的設(shè)計方案:采用通用嵌入式CPU實現(xiàn)的設(shè)計方案;采用FPGA實現(xiàn)的設(shè)計方案;以及采用XCore處理器設(shè)計方案,如圖2所示。

評論