采用高級節點ICs實現從概念到推向消費者的最快途徑(08-100)

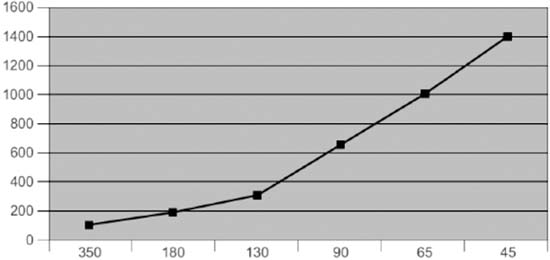

這種良品率優化技術特別適合分級使用,優化“被推薦”規則的利用。目前為止,設計師對于有效應對被推薦的規則集沒有多少選擇。據圖4所示規則組大小的爆炸性增加,使用傳統工具的定制設計布局團隊,僅在應對必要規則方面就面臨著巨大的挑戰。結果,布局工程師經常在創建物理設計時忽略被推薦的規則,導致良品率沒有實現最優化。作為選擇,工程師可能會挑選一些被推薦的規則,并強制性地考慮他們——這種方法通常犧牲了芯片面積與性能。其他方法僅提供了部分解決方案,試圖應用手動方法或者簡單的DRC式方法,在一些重要的標準模塊中采用被推薦的規則。通過全面的Cadence良品率優化法,比起先前的其他方法,設計可以實現對被推薦規則更高的一致性。

本文引用地址:http://www.czjhyjcfj.com/article/91700.htm核心設計規則數量

圖4 為了讓工廠使用當今的193納米波長步進電機印刷45納米功能,設計師在物理設計的過程中,必須遵照其創造的關于形狀與間距的更多限制性規則。

從概念到推向消費者的最快途徑

在半導體公司探索45納米技術優勢的過程中,設計師將會面臨制造影響對設計性能越來越大的沖擊。結合業界頂尖的定制與數字設計流程,Cadence高級節點設計(Cadence Advanced Node Design)解決方案提供了一種端到端的方法,提供同步的簽收質量可制造性分析與實現。經過實際制造證明的Cadence,基于模型與規則的方法,迅速而全面地提供精確的結果,讓設計師更加可靠地預測芯片性能,即便各種新的影響大大提升了高級節點IC設計的挑戰。Cadence解決方案提供了一種完整的設計到制造的解決方案,囊括了開發、物理實現、簽收和制造。使用這種環境,半導體公司可以加快復雜高級節點IC的量產時間。

[CDSI1]Cadence Space-Based Router

電機保護器相關文章:電機保護器原理

評論