高成本效益的實用系統方法解決QFN-mr BiCMOS器件單元測試電源電流失效問題

摘要

本文引用地址:http://www.czjhyjcfj.com/article/201703/344836.htm本文探討一套解決芯片單元級電測試過程電源電流失效問題的方法。當采用QFN-MR(四邊扁平無引線–多排引腳封裝)的BiCMOS (雙極互補金屬氧化物半導體)芯片進入量產預備期時,電源電流失效是一個進退維谷的制造難題。

本文介紹了數種不同的失效分析方法,例如,數據分析、實驗設計(DOE)、流程圖分析、統計輔助分析和標桿分析,這些分析方法對確定問題的根源有很大的幫助,然后使用統計工程工具逐步濾除可變因素。

本項目找到了電流失效問題的根源,并采用了相應的解決措施,使電源電流失效發生率大幅降低,與主要競爭對手旗鼓相當。最終,這個項目只通過優化公司內部資源,就提高了封裝測試總體良率,而沒有增加額外制造成本。

這些改進措施還提高了產品質量,降低了客戶投訴質量問題的風險。在全部解決措施落實到位后,隨著量產成功,該項目節省制造成本38.25萬美元。

1.0 前言

為了能夠在技術快速變化的半導體工業中生存,不管是企業內部用戶,還是外部市場客戶,半導體廠商必須在客戶心目中樹立良好的形象,這是半導體企業保持市場競爭力和品牌價值所面臨的最大挑戰。“滿意度”是建立良好客戶關系的關鍵要素。相反,不能讓客戶滿意的業務是無法持續下去的。

QFN-MR(四邊扁平無引線–多排引腳封裝)是意法半導體卡蘭巴工廠產量的最大的產品,對公司財務業績貢獻率很高(按照全球評估標準)。

不過,為同一客戶生產同一產品,有些外包廠(外包廠1和外包廠2)在產品質量上卻更勝一籌,這迫使卡蘭巴工廠必須自我改進。

產品1是QFN-MR產品,在量產預備階段,電測試電源電流總失效率不合格,總良率損失達到5.2%。產品 1是意法半導體卡蘭巴工廠的一個新產品線,需要給大客戶留下交貨快的印象,但是不能犧牲產品質量,因此,需要找到造成產品缺陷的主要原因。事實上,解決這些問題將會給卡蘭巴工廠量產類似產品平臺帶來改良機會。

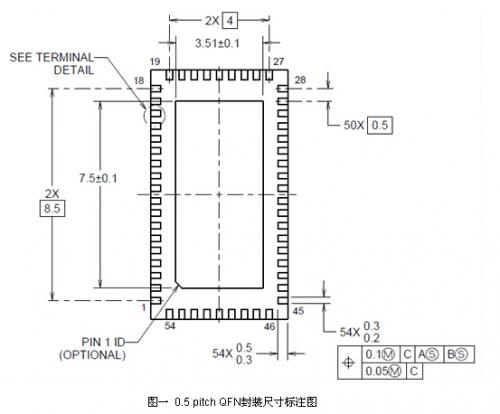

1.1 產品1配置

產品1是一款采用VPLGA封裝的BiCMOS芯片,用于控制硬盤驅動器的電機運行。這里VPLGA代表超薄格柵陣列四邊扁平無引線–多排引腳塑料封裝,封裝厚0.90 mm,引腳88個。目標應用包括纖薄型電子設備和計算機硬盤驅動器的電機控制。

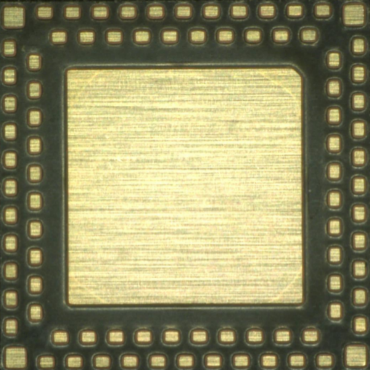

圖1是產品1的封裝示意圖。

圖1:VPLGA88產品配置 / POD

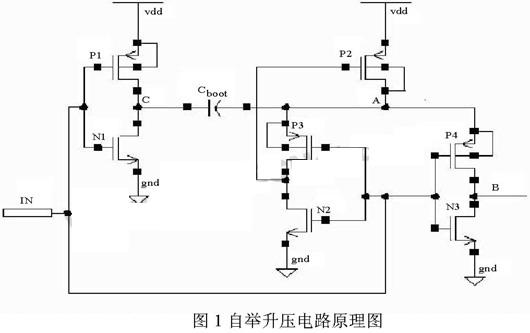

1.2 BiCMOS半導體制造技術

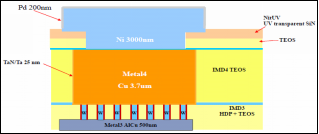

圖2:BiCMOS半導體制造技術

BiCMOS芯片由五層組成。NiPd (鎳鈀金)是最后一層金屬層,互連線就打在這一層上。

1.3 QFN-MR無膠帶引線框架封裝

無膠帶四邊扁平無引線封裝是一種引線框架封裝載體(平臺),利用后工序蝕刻,在載體上形成引腳面積。與其它的類似微型封裝相比,無膠帶QFN封裝給意法半導體卡蘭巴工廠帶來更好實惠,例如,引線框架成本低,支持多排引腳,兼容銅線,無膠帶載體,晶片切割速度快。

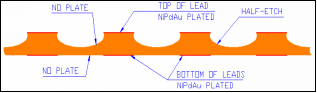

圖3:無膠帶QFN引線框架配置

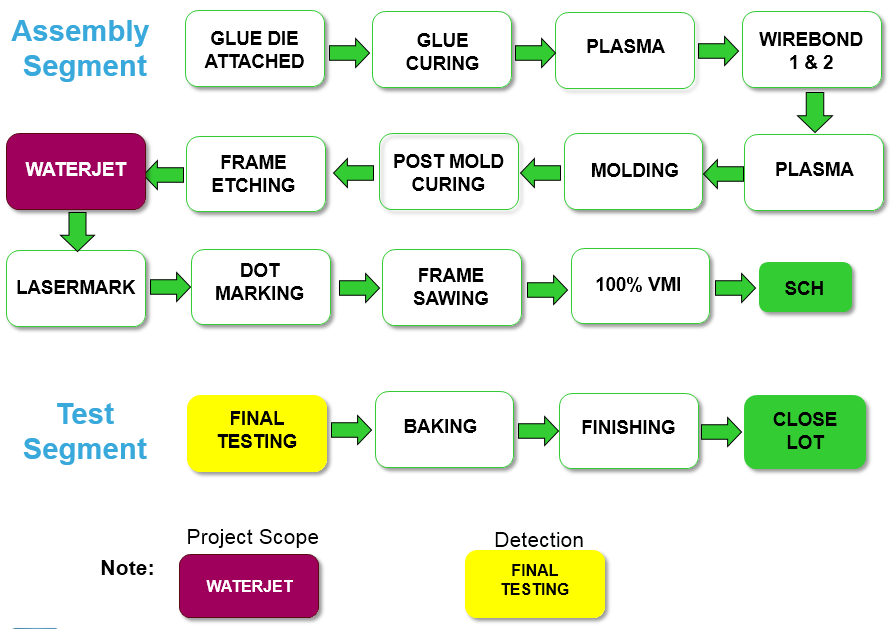

1.4 產品1封測全部流程

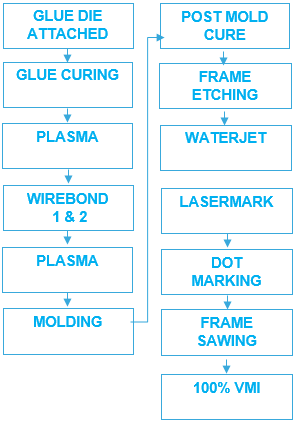

圖4:1.4 產品1封裝流程

圖4所示是產品1的封裝流程,該流程在產品開發和認證測試階段制訂,基于現有封裝流程,采用相同的芯片制造技術和材料。

1.5 產品1線路應力表現

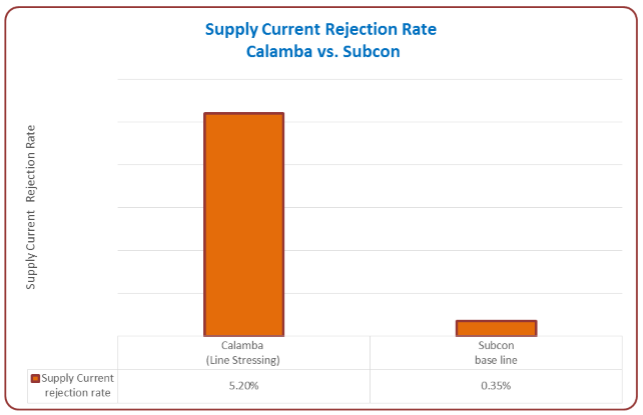

圖5:電源電流抑制比對比

在產品1量產預備初期,最終測試的電源電流抑制比是5.20%,遠超外包廠的0.35%。上面的柱形圖是意法半導體卡蘭巴工廠與外包廠的電源電流抑制比的比較圖,兩者之間的巨大差距對意法半導體卡蘭巴工廠的未來業務發展構成重大威脅。

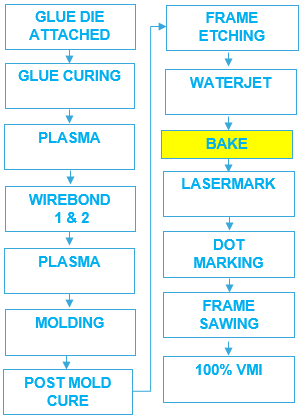

1.6 標桿分析和比較分析

運用標桿分析和比較分析法尋找意法半導體卡蘭巴與外包廠在產品制造上的不同之處。需要說明的是,外包廠在水刀工序后還有烘烤工序。

圖6:意法半導體與外包廠的制造流程比較

在開始分析的時候,我們發現烘烤工序是主要不同之處。在清洗等濕法工序后,需要進行烘烤工序,除掉單元內

的濕汽。初步分析結果顯示,烘烤是最終測試電源電流失效的主要因素,就是這個巨大發現讓項目組開始專注這個工序的探究。

同樣地,項目組還做了微流程圖,以確定項目探究范圍。

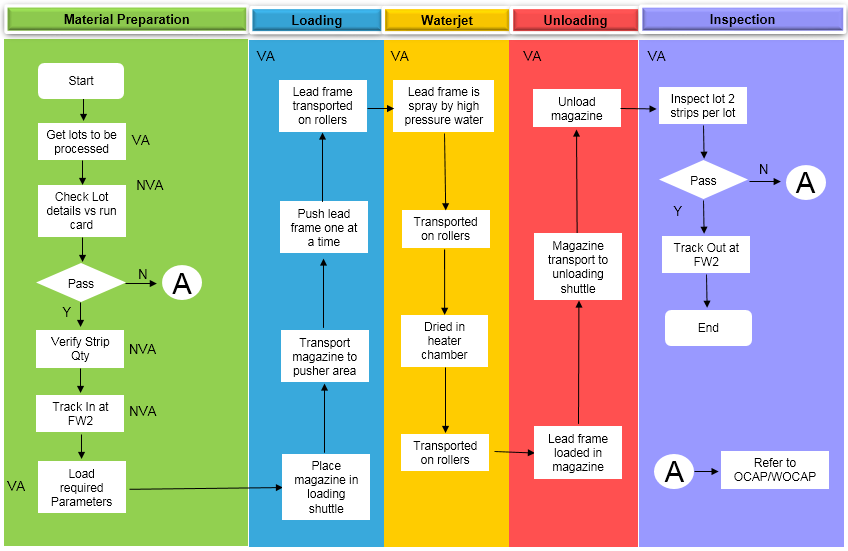

圖7:微流程圖分析/封裝流程圖

1.7 問題描述

在量產預備期,產品1電源電流抑制比是 5.20%,被歸為封裝工序固有濕法工序造成的潮濕性風險。

2.0 實驗部分

2.1 材料:

§ 水刀

§ QFN無膠帶引線框架封裝

§ BiCMOS晶片

§ 塑料單元

§ 檢查與測試設備

2.2 實驗重點放在主要根源即水刀工序上:

確定問題根源并采取相應的糾正措施至關重要,研究方向主要放在濕法工序上,基于微流程圖分析,水刀工序最有可能是潛在變異的根源。

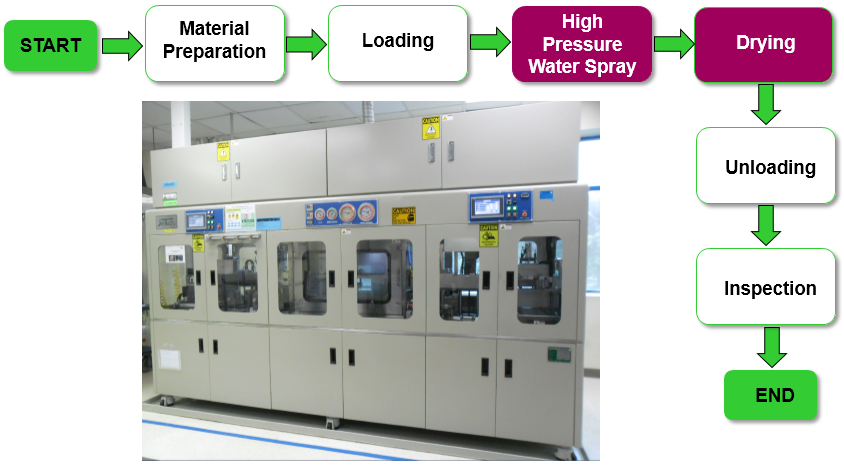

2.3 剖解水刀工序:

為更好地了解水刀工序,需要逐步分析記錄點,觀察從材料制備、裝卸到檢查的整個單元工序。

圖8:水刀工序詳細流程

2.4 識別輸入變化:

運用輸入輸出方法深挖變化因素。經過深入研究,42個KPIV變量被確定為重要的X因素,如圖9所示。(詳圖見附錄A)

圖9:輸入-輸出工作單

2.5 優先考慮因果關系:

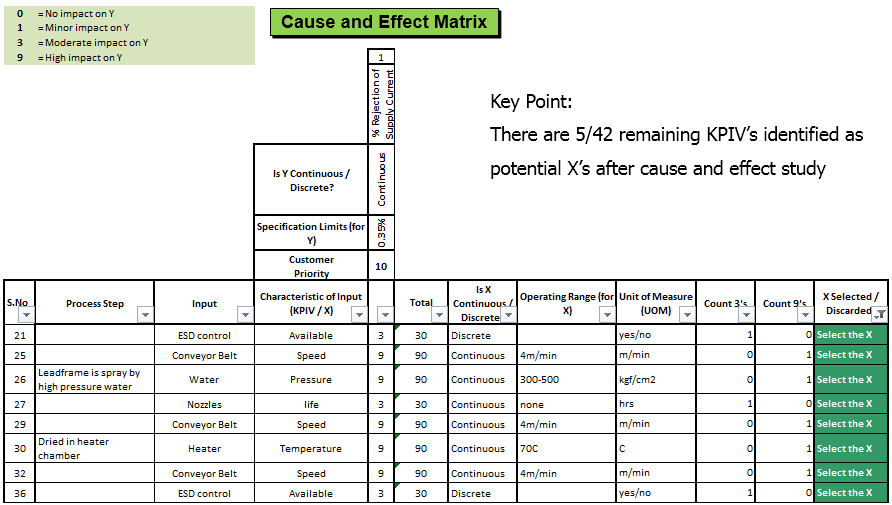

運用因果(C&E)矩陣確立輸入變量與X因素的內部關系,如圖10所示。

(詳圖見附錄B)

圖10:因果矩陣

評論