Vivado IPI 為 Aurora 設計開放 FPGA 共享資源

賽靈思的 IP Integrator 工具可幫助您改善設計輸入生產力和多核 Aurora 設計的資源優化。

本文引用地址:http://www.czjhyjcfj.com/article/201601/286363.htm作者:

K Krishna Deepak

賽靈思高級設計工程師

kde@xilinx.com

Dinesh Kumar

賽靈思高級工程經理

dineshk@xilinx.com

Jayaram PVSS

賽靈思高級工程經理

jayaram@xilinx.com

Ketan Mehta

賽靈思高級IP產品經理

ketanm@xilinx.com

客戶在必須由單個 FPGA 實現的大型設計中使用多個知識產權 (IP) 實例時,面臨的主要挑戰之一是如何在整個系統中有效共享資源。賽靈思 Aurora 串行通信內核的共享邏輯特性使用戶可以在多個實例中共享資源。Vivado 設計套件中的 IP Integrator 工具對于充分利用共享資源至關重要。

電子行業正快速轉向高速串行連接解決方案,同時逐漸舍棄并行通信標準。行業標準串行協議具有固定的線路速率和確定的信道寬度,有時無法充分利用千兆位串行收發器的功能。

Aurora 是賽靈思的高速串行通信協議,一直在行業內非常受歡迎。當某些應用領域中的行業協議實現過程太過復雜或者太耗費資源時,Aurora 通常是首選方案。Aurora 能實現低成本、高數據速率的可擴展IP解決方案,可用于靈活地構建高速串行數據通道。

需要同時對線路速率和通道寬度進行擴展的高性能系統和應用正在期待將 Aurora 作為解決方案。此外,Aurora 還被應用于 ASIC 設計以及包含多塊 FPGA 的系統(用背板傳輸千兆位的數據)中。Aurora 采用簡單的幀結構,并具有協議擴展流量控制功能,可用于封裝現有協議的數據。它的電氣要求與產品設備兼容。賽靈思提供 Aurora 64b66b 和 Aurora 8b10b 內核,作為 Vivado 設計套件 IP 目錄的一部分。

Vivado IP Integrator (IPI) 是用于復雜多核系統中資源優化的重要工具。就這一點而言,IPI 將幫助您充分利用 Aurora 64b66b 和 Aurora 8b10b 內核中的共享資源,尤其是“共享邏輯”特性。為了方便起見,我們重點介紹 Aurora 64b66b IP,同時您要了解類似技術也適用于 Aurora 8b10b 內核。

AURORA 的共享資源一覽

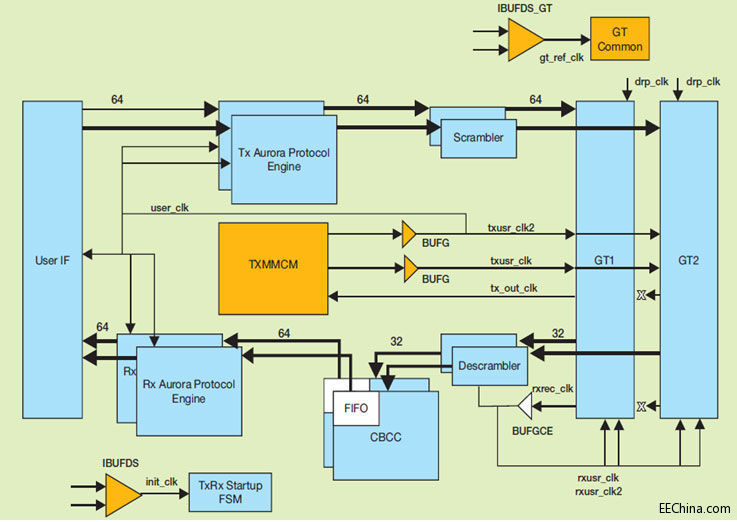

圖 1 是 Aurora 64b66b 內核的典型方框圖。突出顯示部分為時鐘資源,例如混合模式時鐘管理器 (MMCM)、BUFG 和 IBUFDS;以及千兆位收發器 (GT) 資源,例如 GT common 和 GT 通道,在圖中標示為賽靈思 7 系列器件雙路設計的 GT1 和 GT2。

圖 1–用橙色突出顯示的 Aurora 64b66b 內核中的共享資源

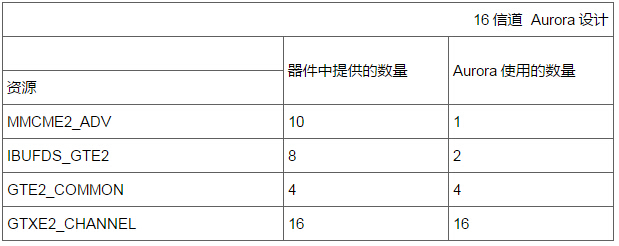

就像 Kintex-7 FPGA KC705 評估套件那樣,典型 16 路 Aurora 64b66b 內核所需的時鐘和 GT 資源已在表 1 中列出。

FPGA 中的時鐘和 GT 資源取決于所選的器件和封裝類型。多個 IP 內核經常要求在系統級使用資源。因此,必須要優化利用這些寶貴資源,以降低系統成本和功耗。

IPI 工具將內核作為頂層模塊進行可視化;標準接口之間的連接現在更加直觀和智能化,在有些情況下甚至可實現自動化。正確的設計規則檢查被置入工具以及 IP 周圍,以確保突出顯示錯誤連接,以便設計人員在設計輸入時發現它們。該工具能自動生成頂層封裝文件以及調用正確的引腳級 I/O 要求,因此可幫助系統設計人員提高生產力。如果您已經設計了定制子模塊,可以考慮

AURORA 資源共享

因為多款基于 GT 的賽靈思內核都支持共享邏輯特性,Aurora 內核可配置為“內核(主機)中的共享邏輯”或“實例設計(從機)中的共享邏輯”。當在系統級進行實例化時,兩種配置的組合可支持在主機與從機之間共享時鐘和 GT 資源。

對于需要使用共享邏輯特性的應用,手動建立多個 IP 之間的連接有可能會產生錯誤,并增加總的設計輸入時間。借助工具進行設計輸入是一種解決該問題的方法,而賽靈思的 IP Integrator 能游刃有余地完成這個任務。

依照賽靈思應用指南 1168,“針對 Vivado IP Integrator 打包定制 AXI IP”(XAPP1168) 對設計進行打包,并在 IPI 中使用子模塊。

Aurora 的共享邏輯特性不僅可讓用戶在多個實例中共享資源,而且還能在相同 GT Quad 封裝中使用 GT 通道,無需編輯 GT common、PLL、時鐘以及相關模塊。唯一的約束是“共享”內核的線路速率應該相同(允許存在諧波,只要您能接受其對時鐘資源的影響即可)。

典型的共享邏輯設計在一個 Guad 中包含一個主機以及一個或多個從機實例。與大多數其它通信 IP 不同,Aurora不僅限于單個 Guad 共享。Aurora 內核的共享邏輯定義可擴展用于任意數量的受支持信道。

下面的一些實例展示了 Aurora 共享邏輯特性的應用情況。

多個單信道設計

單部 FPGA 中的多個單信道設計與多信道設計的不同之處在于前者需要通道綁定。我們可以直觀地看到多個單信道設計所需的資源會在系統級線性增加。讓我們考慮不同情況,并了解共享邏輯特性如何在每種情況下起作用。

我們首先從包含四條單信道的設計開始。通過實例化四個單信道 Aurora 內核,您可直接構建這類設計。如果我們實際執行該實現方案,會發現每個 Aurora 設計都有一個 GT common 實例;因此,該設計的布局和資源利用會遍及四個 GT Guad。這種方法消耗太多資源,不一定總是可行。

表 1–Kintex-7 FPGA KC705 評估套件上的時鐘和 GT 資源利用率

為實現更好的布局以及在功耗和資源方面精心優化的解決方案,所選的四個 GT 應來自同一個 GT Guad。

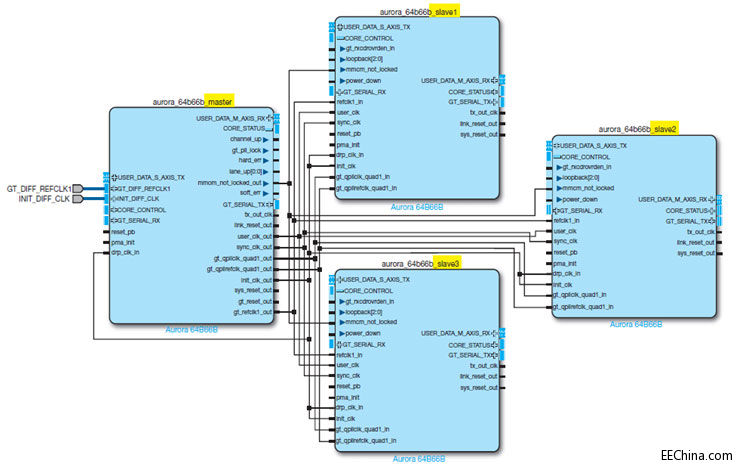

如果沒有共享邏輯特性,而是通過手動處理所生成的設計來滿足該要求,需要花費很大精力。要想有效使用共享邏輯特性,您需要生成一個主機模式的 Aurora 內核以及其它三個從機模式的 Aurora 內核,如圖 2 所示。另外,還有一些其它的系統級考慮因素,例如主機內核控制了進入從機內核的時鐘,所以需要對內核復位。只有用相同的線路速率配置 Aurora 內核,才能立即實現這種配置和資源優化。表 2 定量地說明了在系統中為四個單信道設計使用共享邏輯特性所能實現的優勢。

圖 2–使用一個主機 Aurora 內核(左)和三個從機的共享邏輯設計

占用 12 個 GT 通道的設計

對于 7 系列 FPGA 而言,基于南北時鐘的要求是如果從中間 Guad 中選擇單個參考時鐘源,其最多可服務 12 個 GT 通道。

讓我們考慮下這種使用情況,其需要 12 個單信道設計使用盡可能少的時鐘資源。

如果您將圖 2 所示的“一個主機加三個從機”配置進行延伸,便可節省時鐘資源。如果將這種 1+3 配置延伸為三個 Guad,那么設計一共需要六個差分時鐘資源。不過,如果您選擇讓其中兩個主機設計接受一個單端 INIT_CLK 和一個 GT 參考時鐘,那么還能節省更多資源。這樣我們可將該系統的差分時鐘輸入從六個減少至兩個,從而節省 IBUFDS/IBUFDS_GTE2 資源需求(參見表 3)。設計中的 IBUFDS_GTE2 資源節省實際上還意味著可以節省外部時鐘資源以及設計管腳。

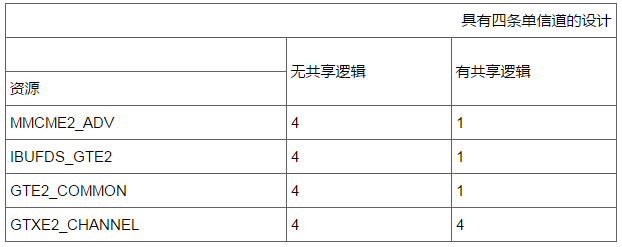

表 2–在包含四條單信道的設計中使用共享邏輯所實現的資源利用率優勢

此外,還可針對 MMCM 進行類似的優化。

表 3–在包含 12 條單信道的設計中使用共享邏輯功能所實現的資源優勢

評論