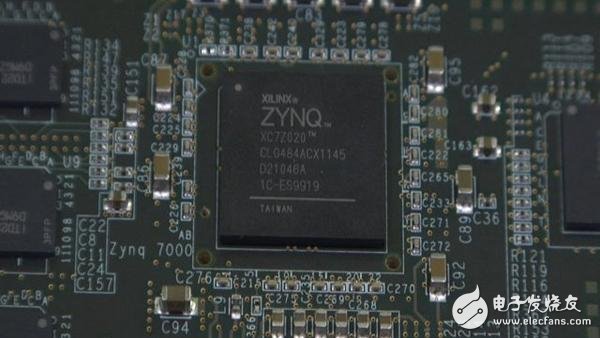

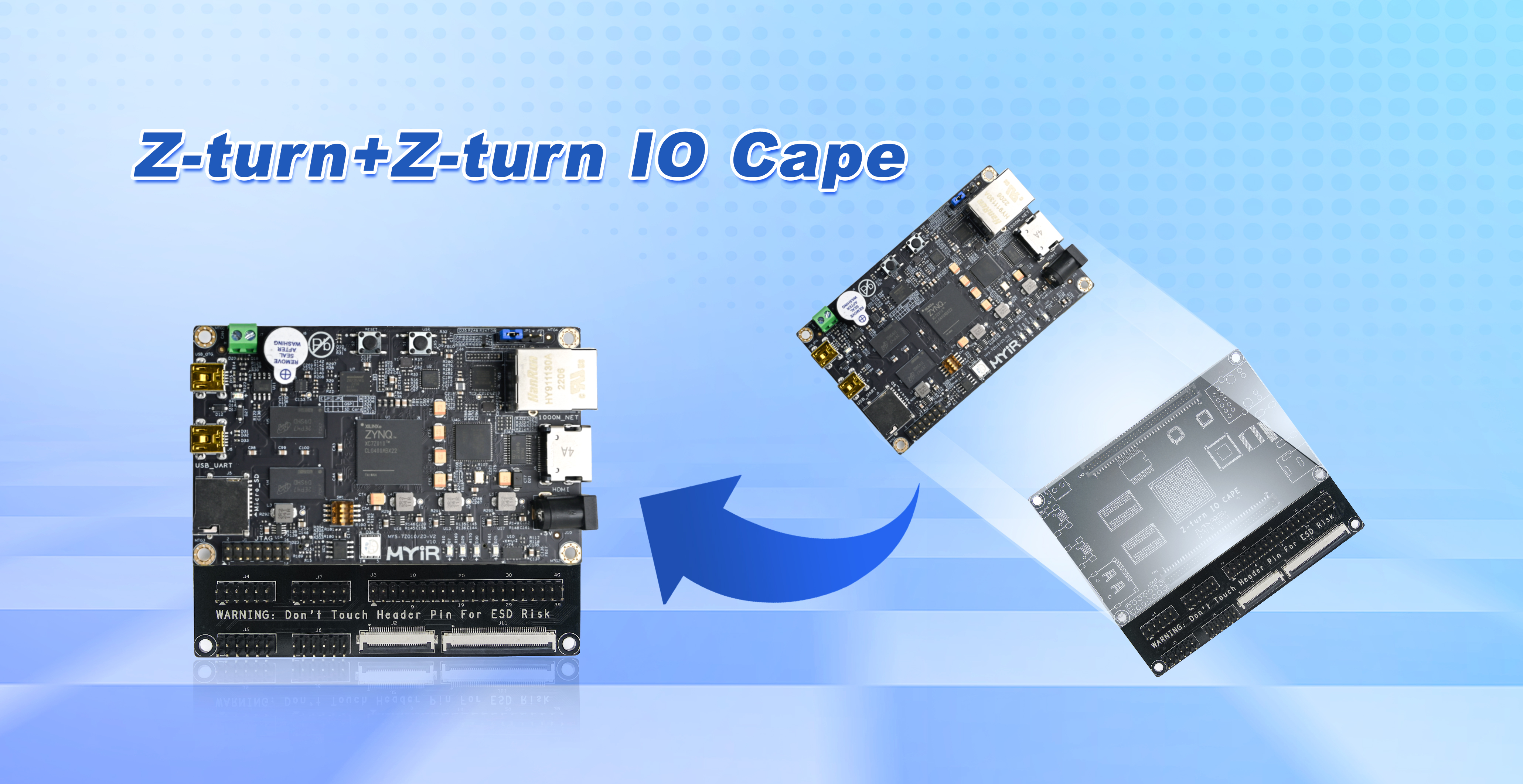

創建ZYNQ處理器設計和Logic Analyzer的使用

我們的目的是創建一個Zynq Soc處理器設計,并用Logic Analyzer來調試我們感興趣的信號。

本文引用地址:http://www.czjhyjcfj.com/article/201710/365490.htm首先,打開Vivado,創建一個工程。

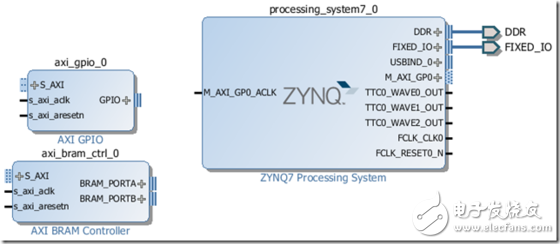

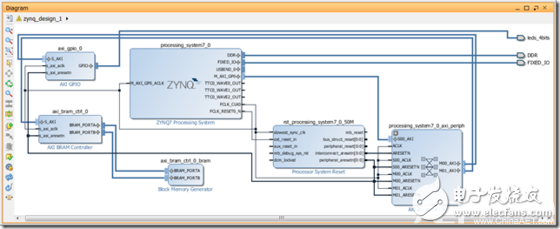

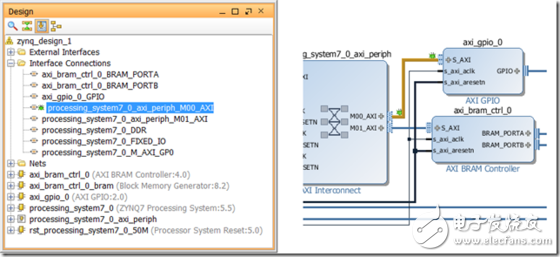

添加這幾個IP核,

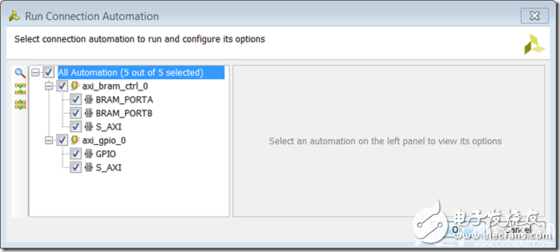

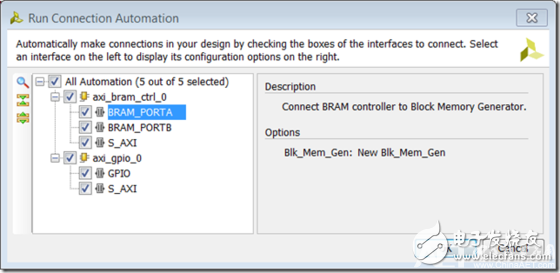

點擊Run ConnecTIon AutomaTIon,讓軟件自動幫我們連起來。在打開的對話框中選擇ALL AutomaTIon,

ok,軟件自動連接起來,

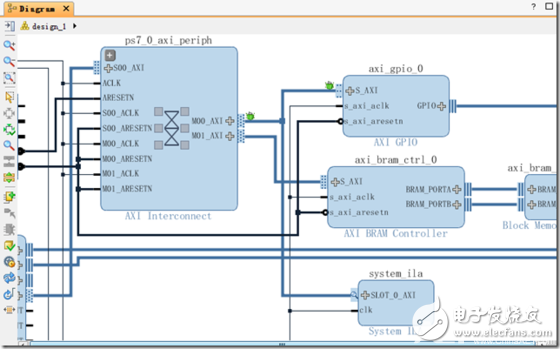

如果要觀察感興趣的信號,這里先右鍵--Generate Output Products,Create HDL Wrapper,編譯,執行完成后,選擇感興趣的信號,右鍵-Mark,

那么Block框圖中會有變化,如圖,兩只蟲,

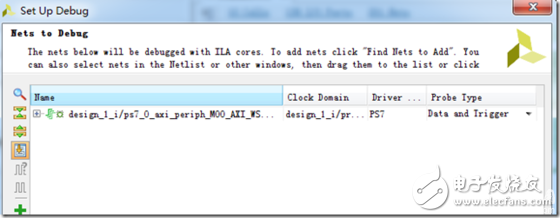

執行Set Up Debug,剛才標記的信號就會出現,

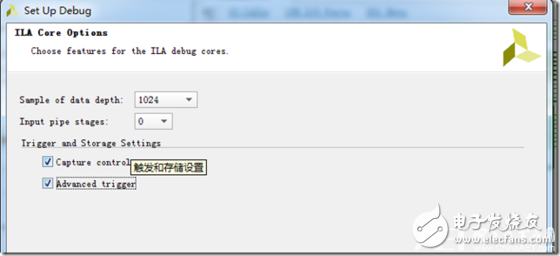

next,進行設置采樣深度,

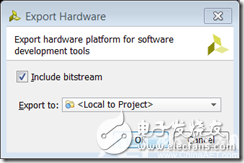

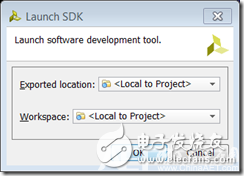

接著執行Implement Design 和 Generate Bitstream。完成后導出到SDK,

未完待續。。。

評論