一種基于PLL的P波段可控頻率源

摘要:介紹了一種P波段可控頻率源的設計方案和相關理論,采用PLL即鎖相技術實現P波段的頻率產生,具有相位噪聲低,雜散低的特點。利用單片機作為數據處理核心對鎖相環的鑒相器進行置數和控制,實現了480~540MHz、步進為1MHz的可控頻率輸出。該頻率源的主要性能指標為:輸出頻率480~540MHz,頻率步進為1MHz,相位噪聲優于-82dBc@1kHz,雜散抑制優于-60dBc,鎖相環直接輸出功率為0.6~1.1dBm。

本文引用地址:http://www.czjhyjcfj.com/article/164388.htm頻率源作為電子系統的核心,是決定電子系統性能的關鍵設備。雷達、通信、電子偵察和對抗設備中,高性能的頻率源是實現其整體設備高性能指標的關鍵技術之一。頻率源的相位噪聲和雜散抑制的性能直接影響整個系統的性能。其中采用鎖相環設計的頻率源具有輸出頻率高、頻率穩定度高、頻率純、低相噪、雜散抑制好等優點。

鎖相環的基本原理

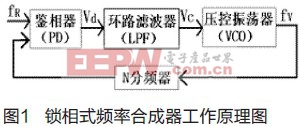

PLL(鎖相環)是一種反饋控制電路,PLL在工作的過程中,當輸出信號的頻率與輸入信號的頻率相同時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是PLL名稱的由來。PLL通常由鑒相器(PD)、環路濾波器(LF)和壓控振蕩器(VCO)三部分組成,鑒相器把輸入信號的相位與壓控振蕩器輸出信號的相位進行比較,輸出一個正比于兩個輸入信號相位差的電壓(或者電流)加到環路濾波器上,抑制噪聲和高頻分量后,再加到壓控振蕩器上,控制其頻率變化,使輸入信號與壓控振蕩器信號之間的相位差逐漸減小,最后達到動態鎖定。鎖相環的基本結構如圖1。

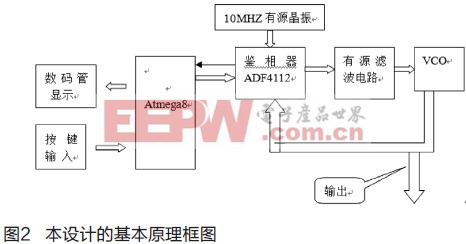

其中N分頻器是由單片機編程控制的,因此這種合成器又體現了程序設計和鎖相技術的結合。從總體結構看,它由單片機、鎖相環和可編程分頻器三部分組成。

電路設計與實現

本設計設計目標是一個可控的鎖相環頻率合成器。因此本電路結合典型鎖相環電路和單片機控制電路,通過單片機改變鎖相環中的鑒相器的分頻比來改變最終的頻率輸出。鎖相環中的低通濾波器采用運算放大器構成的有源低通濾波器。基本設計框圖如圖2。

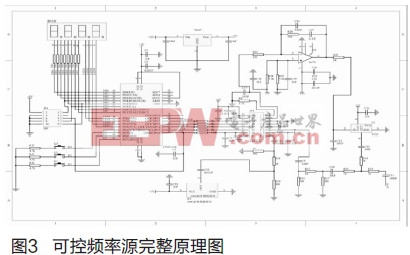

鑒相器我們采用了RU-16封裝的ADF4112,ADF4112是一種直接數字式頻率合成器,它由一個低噪聲的數字相位/頻率檢波器PFD,一個精密的充電泵,一個可編程的參基準分頻器,可編程的A、B計數器,和一個雙模式的前置分頻器(P/P+1)。A(6位)和B(13位)計數器連同雙模式的前置分頻器(P/P+1),能實現一個分頻比為N的分頻器。除此之外,14位的基準計數器(R計數器)允許在PFD的輸入端選擇REFIN的頻率輸入。通過對R、P、A、B的編程可使電路輸出頻率變化。

濾波電路部分我們采用了有源濾波電路,中心器件采用了LM741。VCO(壓控振蕩器)采用中電13所生產的調諧電壓為0~12V,最大輸出頻率為390~547MHz的表面安裝微型集成VCO。單片機我們采用了TQFP封裝的AVR單片機Atmega8,參考晶振采用10MHz有源晶振,顯示采用共陰四聯數碼管。該設計整體電路原理圖如圖3。

可控硅相關文章:可控硅工作原理

低通濾波器相關文章:低通濾波器原理

分頻器相關文章:分頻器原理 塵埃粒子計數器相關文章:塵埃粒子計數器原理 鑒相器相關文章:鑒相器原理 晶振相關文章:晶振原理 鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論