SJ-LDMOST中的襯底輔助耗盡效應

引言

本文引用地址:http://www.czjhyjcfj.com/article/127427.htm橫向功率DMOST(Double-diffused MOS Transistor)器件自從上世紀70年代問世以來,作為多子器件,由于具有高的輸入阻抗、好的關斷特性、易于集成等優點,在許多領域取代傳統的雙極器件得到廣泛的應用。而器件設計中面臨的主要折衷就是擊穿電壓和比導通電阻之間的折衷。對于滿足RESURF(REdued SURface Field)條件[1]的常規橫向高壓DMOST,其比導通電阻與擊穿電壓的2.5次方成正比[2],因此,高的導通電阻限制了橫向DMOST器件在高壓領域的應用。縱向超結結構(Super Junction,SJ)將器件比導通電阻與擊穿電壓之間的次方關系由2.5降低到1.1[3]。所以,近年來,將超結引入橫向功率器件設計成為業界廣泛關注和研究的熱點之一。

襯底輔助耗盡效應機理

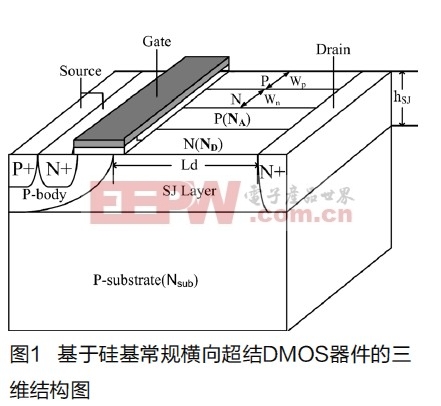

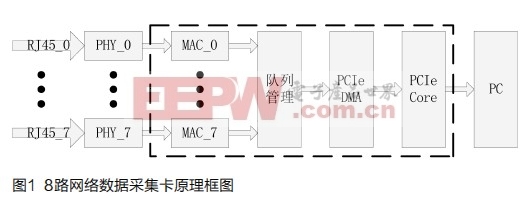

縱向超結結構同時兼具高耐壓、低導通電阻特性,但當將超結思想引入橫向DMOST時,設計中首先面臨的是消除襯底輔助耗盡效應(Substrate-Assisted-Depletion Effect)[4]。圖1為基于硅基常規橫向超結DMOS器件的三維結構圖。由該圖可以看出,常規LDMOS的N-漂移區被相間的高摻雜濃度P型和N型柱區所代替。關態時,電荷嚴格平衡的P型與N型柱區相互耗盡,產生較高電場,因而承擔高的擊穿電壓;開態時,高摻雜濃度的N型區提供了一個低導通電阻的電流通道。但對于橫向DMOS器件,由于P襯底和N柱區之間的相互耗盡,打破了N柱區和P柱區之間嚴格的電荷平衡,使得P柱區中出現過剩空穴,這種N柱區和P柱區之間電荷的不平衡又進一步嚴重惡化了SJ區的擊穿電壓[5],即橫向擊穿電壓。

襯底輔助耗盡效應的消除

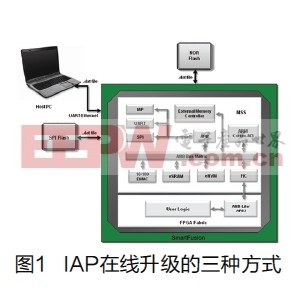

由上述襯底輔助耗盡效應機理分析知:有限大小電阻率的P型襯底對N柱區的耗盡使得P柱區出現了過剩載流子。消除襯底輔助耗盡效應主要有如下兩類:①選用電阻率為無窮大的特殊襯底;②引入額外的N型區以補償P型區中的過剩載流子。

電荷放大器相關文章:電荷放大器原理

評論