EEPW首頁(yè) >>

主題列表 >>

ucie ip

ucie ip 文章 最新資訊

奎芯科技:致力于打通Chiplet設(shè)計(jì)到封裝全鏈條

- 過(guò)去幾年,國(guó)際形勢(shì)的變化讓壯大中國(guó)芯片設(shè)計(jì)產(chǎn)業(yè)成為中國(guó)半導(dǎo)體產(chǎn)業(yè)發(fā)展的主題,伴隨著全社會(huì)對(duì)中國(guó)半導(dǎo)體產(chǎn)業(yè)的關(guān)注提升和資本的涌入,整個(gè)半導(dǎo)體設(shè)計(jì)產(chǎn)業(yè)鏈迎來(lái)全面的發(fā)展機(jī)遇。對(duì)中國(guó)集成電路設(shè)計(jì)產(chǎn)業(yè)來(lái)說(shuō),芯片設(shè)計(jì)能力的提升,不僅需要設(shè)計(jì)公司技術(shù)的提升,還需要先進(jìn)的本土芯片制造能力和相關(guān)設(shè)計(jì)工具的鼎力支撐。 隨著國(guó)內(nèi)芯片設(shè)計(jì)企業(yè)的大量涌現(xiàn),本土芯片設(shè)計(jì)帶動(dòng)著設(shè)計(jì)IP需求增長(zhǎng)非常明顯,這不僅給成立多年的本土IP企業(yè)發(fā)展的黃金機(jī)遇,同時(shí)也催生出大量的新興IP初創(chuàng)企業(yè),這些企業(yè)的起點(diǎn)高、IP運(yùn)作經(jīng)驗(yàn)豐富,共同為

- 關(guān)鍵字: 奎芯科技 Chiplet IP ICCAD

自成一派?這次中國(guó)擁有了屬于自己的Chiplet標(biāo)準(zhǔn)!

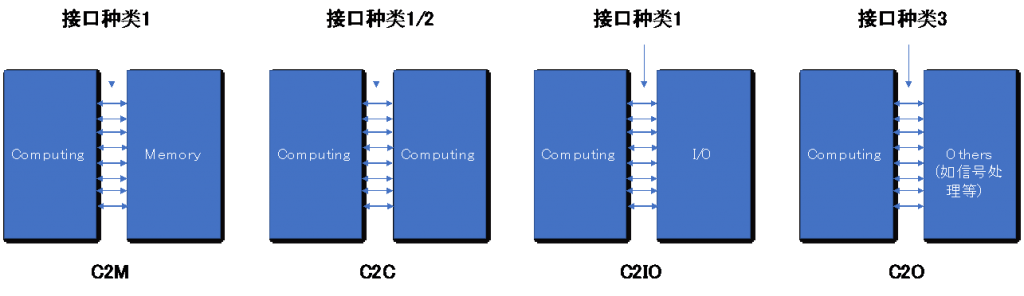

- 每當(dāng)芯片行業(yè)中出現(xiàn)一個(gè)新的技術(shù)趨勢(shì)時(shí),制定規(guī)則的幾乎都是歐美大廠,在概念和技術(shù)的領(lǐng)先優(yōu)勢(shì)下,其他人只能跟在后面按照規(guī)則玩游戲。但這一次,中國(guó)推出了自己的Chiplet(小芯片)標(biāo)準(zhǔn)。12 月 16 日,在 “第二屆中國(guó)互連技術(shù)與產(chǎn)業(yè)大會(huì)”上,首個(gè)由中國(guó)集成電路領(lǐng)域相關(guān)企業(yè)和專(zhuān)家共同主導(dǎo)制定的《小芯片接口總線技術(shù)要求》團(tuán)體標(biāo)準(zhǔn)正式通過(guò)工信部中國(guó)電子工業(yè)標(biāo)準(zhǔn)化技術(shù)協(xié)會(huì)的審定并發(fā)布。據(jù)介紹,這是中國(guó)首個(gè)原生 Chiplet 技術(shù)標(biāo)準(zhǔn)。Chiplet,芯片界的樂(lè)高簡(jiǎn)單表述一下什么是Chiplet。借用長(zhǎng)江證券研報(bào)

- 關(guān)鍵字: chiplet 小芯片 UCIe

對(duì)標(biāo)AMD、Intel 中國(guó)首個(gè)原生Chiplet小芯片標(biāo)準(zhǔn)發(fā)布

- 由于摩爾定律放緩,芯片工藝雖然在進(jìn)步,但集成的晶體管密度無(wú)法翻倍式提升,AMD、Intel等公司已經(jīng)推出了Chiplet小芯片架構(gòu),將多種芯片集成在一起,現(xiàn)在中國(guó)首個(gè)原生Chiplet小芯片標(biāo)準(zhǔn)也正式發(fā)布了。據(jù)報(bào)道,在16日舉辦的“第二屆中國(guó)互連技術(shù)與產(chǎn)業(yè)大會(huì)”上,首個(gè)由中國(guó)集成電路領(lǐng)域相關(guān)企業(yè)和專(zhuān)家共同主導(dǎo)制定的《小芯片接口總線技術(shù)要求》團(tuán)體標(biāo)準(zhǔn)正式通過(guò)工信部中國(guó)電子工業(yè)標(biāo)準(zhǔn)化技術(shù)協(xié)會(huì)的審定并發(fā)布。據(jù)悉,這是中國(guó)首個(gè)原生Chiplet技術(shù)標(biāo)準(zhǔn)。小芯片(Chiplet,又名芯粒)技術(shù),是一種模塊化芯片技術(shù)

- 關(guān)鍵字: chiplet 小芯片 UCIe

Codasip 宣布成立 Codasip 實(shí)驗(yàn)室,以加速行業(yè)前沿技術(shù)的開(kāi)發(fā)和應(yīng)用!

- 德國(guó)慕尼黑,2022年12月7日——處理器設(shè)計(jì)自動(dòng)化和RISC-V處理器IP的領(lǐng)導(dǎo)者Codasip今日宣布成立Codasip實(shí)驗(yàn)室(Codasip Labs)。作為公司內(nèi)部創(chuàng)新中心,新的Codasip實(shí)驗(yàn)室將支持關(guān)鍵應(yīng)用領(lǐng)域中創(chuàng)新技術(shù)的開(kāi)發(fā)和商業(yè)應(yīng)用,覆蓋了安全、功能安全(FuSa)和人工智能/機(jī)器學(xué)習(xí)(AI/ML)等方向。該實(shí)驗(yàn)室的使命在于識(shí)別和構(gòu)建相關(guān)技術(shù),以擴(kuò)展定制計(jì)算的可能性,并加快具有定制化的、領(lǐng)域?qū)S迷O(shè)計(jì)的差異化產(chǎn)品的開(kāi)發(fā),并縮短其上市時(shí)間。Codasip實(shí)驗(yàn)室將由公司創(chuàng)始人兼總裁馬克仁(Ka

- 關(guān)鍵字: Codasip Codasip 實(shí)驗(yàn)室 IP RISC-V

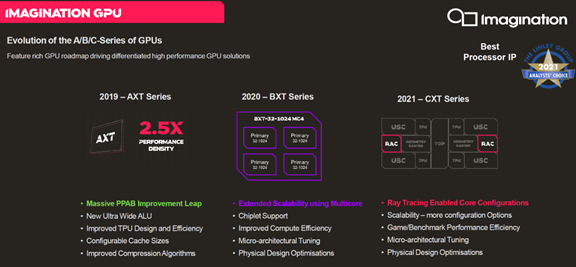

“倒金字塔”折射IP巨大價(jià)值,Imagination IP創(chuàng)新蝶變賦能半導(dǎo)體產(chǎn)業(yè)

- 過(guò)去50余年,芯片制程迭代沿著摩爾定律滾滾向前,并持續(xù)增強(qiáng)著芯片的算力與性能。現(xiàn)如今,無(wú)論是在SoC上集成越來(lái)越多的功能模塊,又或是利用chiplet技術(shù)在先進(jìn)制程下進(jìn)一步提升芯片集成度,都充分展現(xiàn)了芯片性能、功耗和成本的改進(jìn)不能僅僅依賴于制程的升級(jí),而需從不同的維度拓展創(chuàng)新來(lái)延續(xù)摩爾定律的“經(jīng)濟(jì)效益”。這導(dǎo)致芯片設(shè)計(jì)變得越來(lái)越困難,IP的作用也愈加凸顯,逐漸成為企業(yè)尋求設(shè)計(jì)差異化道路上的“秘鑰”。?日前,在深圳舉辦的第10屆EEVIA年度中國(guó)硬科技媒體論壇暨產(chǎn)業(yè)鏈研創(chuàng)趨勢(shì)展望研討會(huì)上,Imag

- 關(guān)鍵字: IP Imagination

Imagination:SoC IP技術(shù)賦能未來(lái)硬核科技創(chuàng)新

- 在龐大的半導(dǎo)體細(xì)分產(chǎn)業(yè)鏈中,IP是其中最特殊的一環(huán)。正是借助眾多的IP,才讓半導(dǎo)體發(fā)展的步伐如此之快。IP是整個(gè)半導(dǎo)體上游產(chǎn)業(yè)鏈里面的核心,根據(jù)統(tǒng)計(jì)數(shù)據(jù)可以發(fā)現(xiàn),每一元芯片能撐起200多元的社會(huì)經(jīng)濟(jì),而每一元的IP,能支持20000元的社會(huì)經(jīng)濟(jì)價(jià)值,所以IP公司的存在是必要的。 隨著芯片復(fù)雜度不斷提升,特別是芯片進(jìn)入SoC時(shí)代使得系統(tǒng)對(duì)各個(gè)環(huán)節(jié)技術(shù)要求越來(lái)越高,對(duì)一些中小型公司、創(chuàng)業(yè)公司來(lái)說(shuō),他們需要在成長(zhǎng)過(guò)程中專(zhuān)注核心領(lǐng)域,沒(méi)辦法提供整個(gè)SoC完整的技術(shù),所以它需要IP公司的支持,IP公司能協(xié)

- 關(guān)鍵字: Imagination SoC IP GPU

燦芯半導(dǎo)體提供MIPI IP完整解決方案

- 中國(guó)上海—2022年10月14日——一站式定制芯片及IP供應(yīng)商——燦芯半導(dǎo)體日前宣布推出可用于客制化ASIC/SoC設(shè)計(jì)服務(wù)的MIPI IP完整解決方案。該解決方案由一系列 MIPI控制器和PHY構(gòu)成。可以幫助系統(tǒng)制造商和IC公司等設(shè)計(jì)高質(zhì)量的ASIC/SoC產(chǎn)品,同時(shí)加速上市時(shí)間。 MIPI聯(lián)盟在2003年成立,MIPI全稱(chēng)Mobile Industry Processor Interface,即移動(dòng)產(chǎn)業(yè)處理器接口。顧名思義,是為了統(tǒng)一和簡(jiǎn)化手機(jī)處理器的接口,CSI、DSI、DigRF、C/D

- 關(guān)鍵字: 燦芯 MIPI IP

proteanTecs加入U(xiǎn)CIe聯(lián)盟,推進(jìn)2.5D/3D互聯(lián)監(jiān)控

- 先進(jìn)電子產(chǎn)品深度數(shù)據(jù)分析領(lǐng)域的全球領(lǐng)先企業(yè)proteanTecs宣布已加入U(xiǎn)CIe?(通用芯粒互聯(lián)技術(shù))聯(lián)盟,將互聯(lián)健康監(jiān)測(cè)引入不斷擴(kuò)大的先進(jìn)封裝生態(tài)系統(tǒng)。 proteanTecs_joins_UCIeUCIe?于2022年3月推出,旨在創(chuàng)建封裝層面的通用互聯(lián),以應(yīng)對(duì)"超越摩爾(More Than Moore)"市場(chǎng)的激增,預(yù)計(jì)到2027年該市場(chǎng)的發(fā)展將達(dá)到19%的復(fù)合年增長(zhǎng)率。1該聯(lián)盟聯(lián)合了行業(yè)領(lǐng)先企業(yè),構(gòu)建一個(gè)具有互操作性的多供應(yīng)商生態(tài)系統(tǒng),并實(shí)現(xiàn)未來(lái)幾代的芯片到芯片

- 關(guān)鍵字: 通用芯粒互聯(lián)技術(shù) proteanTecs UCIe

Achronix收購(gòu)FPGA網(wǎng)絡(luò)解決方案領(lǐng)導(dǎo)者Accolade Technology的關(guān)鍵IP和專(zhuān)長(zhǎng)

- 加利福尼亞州圣克拉拉市,2022年9月19日——高性能現(xiàn)場(chǎng)可編程邏輯門(mén)陣列(FPGA)和嵌入式FPGA(eFPGA)半導(dǎo)體知識(shí)產(chǎn)權(quán)(IP)領(lǐng)域的領(lǐng)導(dǎo)性企業(yè)Achronix半導(dǎo)體公司宣布:該公司已經(jīng)收購(gòu)了Accolade Technology的關(guān)鍵IP資產(chǎn)以及Accolade的技術(shù)團(tuán)隊(duì),此舉使Achronix的客戶能夠更快速且更輕松地設(shè)計(jì)高性能網(wǎng)絡(luò)和數(shù)據(jù)中心系統(tǒng)。Accolade在FPGA的網(wǎng)絡(luò)應(yīng)用方面擁有深厚的專(zhuān)業(yè)知識(shí),此次收購(gòu)使Achronix能夠?yàn)殚_(kāi)發(fā)網(wǎng)絡(luò)技術(shù)的客戶提供強(qiáng)大的硬件和軟件解決方案。“如今

- 關(guān)鍵字: Achronix FPGA Accolade IP

燦芯半導(dǎo)體推出USB IP完整解決方案

- 一站式定制芯片及IP供應(yīng)商——燦芯半導(dǎo)體日前宣布推出可用于ASIC/SoC的USB IP完整解決方案。該解決方案由一系列 USB 控制器和 PHY 構(gòu)成,可以助力系統(tǒng)制造商、個(gè)人電腦原始設(shè)備制造商和 IC公司等設(shè)計(jì)高質(zhì)量的ASIC/SoC 產(chǎn)品。USB(通用串行總線)已經(jīng)非常成功地將打印機(jī)、掃描儀、鍵盤(pán)、鼠標(biāo)、閃存驅(qū)動(dòng)器、操縱桿、相機(jī)和顯示器等硬件連接到各種計(jì)算機(jī),包括智能手機(jī)、臺(tái)式機(jī)、平板電腦和筆記本電腦等。USB4規(guī)范在2019年9月由USB-IF組織執(zhí)行,可支持USB3、Displayport、PC

- 關(guān)鍵字: 燦芯 USB IP

第 150 億顆CEVA 助力芯片出貨

- 全球領(lǐng)先的無(wú)線連接和智能感知技術(shù)及共創(chuàng)解決方案的授權(quán)許可廠商CEVA, Inc.(納斯達(dá)克股票代碼:CEVA)宣布,包含CEVA IP的并支付權(quán)利金的芯片的累計(jì)出貨量已經(jīng)在第二季超過(guò)了150億顆。在上市將近二十周年之際,CEVA達(dá)成了這一重要里程碑。實(shí)現(xiàn)前100億顆CEVA助力的芯片出貨花費(fèi)了超過(guò)15年時(shí)間,而完成隨后50 億顆芯片出貨則只用了不到三年半。 CEVA IP在物聯(lián)網(wǎng)時(shí)代以令人驚訝的速度被廣泛采用也證實(shí)了CEVA在無(wú)線連接的普及方面發(fā)揮了重要的作用。CEVA將5G、蜂窩物聯(lián)網(wǎng)、藍(lán)牙、

- 關(guān)鍵字: CEVA IP

Credo正式推出基于臺(tái)積電5nm及4nm先進(jìn)制程工藝的全系列112G SerDes IP產(chǎn)品

- ?Credo Technology(納斯達(dá)克股票代碼:CRDO)近日正式宣布推出其基于臺(tái)積電5nm及4nm制程工藝的112G PAM4 SerDes IP全系列產(chǎn)品,該系列能夠全面覆蓋客戶在高性能計(jì)算、交換芯片、人工智能、機(jī)器學(xué)習(xí)、安全及光通信等領(lǐng)域的廣泛需求,包括:超長(zhǎng)距(LR+)、長(zhǎng)距(LR)、中距(MR)、超極短距(XSR+)以及極短距(XSR)。?Credo IP產(chǎn)品業(yè)務(wù)開(kāi)發(fā)助理副總裁Jim Bartenslager表示, “Credo先進(jìn)的混合信號(hào)以及數(shù)字信號(hào)處理(DSP)1

- 關(guān)鍵字: Credo 臺(tái)積電 5nm 4nm SerDes IP

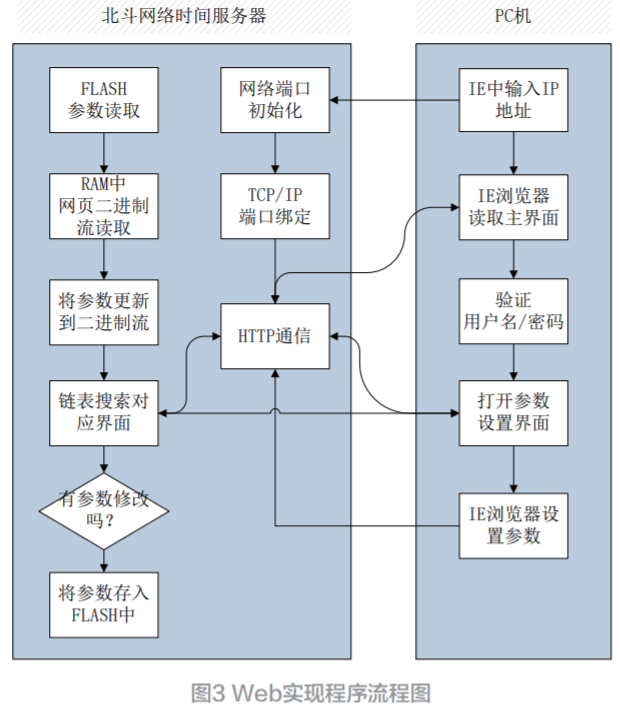

嵌入式北斗網(wǎng)絡(luò)時(shí)間服務(wù)器的Web網(wǎng)頁(yè)實(shí)現(xiàn)

- 摘要:本文介紹了嵌入式北斗網(wǎng)絡(luò)時(shí)間服務(wù)器的基本功能,重點(diǎn)講述了如何在該設(shè)備中添加Web網(wǎng)頁(yè)的方法 及實(shí)現(xiàn)過(guò)程,以及在嵌入式設(shè)備中添加此功能應(yīng)該考慮的資源因素。關(guān)鍵詞:TCP/IP;HTTP;Cortex-M4;RAM;鏈表?1 時(shí)間服務(wù)器功能描述北斗衛(wèi)星接收終端接收北斗導(dǎo)航衛(wèi)星發(fā)射的 RNSS (Radio Navigation Satellite System,無(wú)線導(dǎo)航衛(wèi)星系統(tǒng)) 無(wú)線電波信號(hào),在設(shè)備內(nèi)部通過(guò) PVT 解算,計(jì)算出用 戶當(dāng)前的位置、速度以及時(shí)間信息。北斗的時(shí)間信息具

- 關(guān)鍵字: 202208 TCP/IP HTTP Cortex-M4 RAM 鏈表

Inuitive 與 Arteris IP 合作為邊緣設(shè)備 提供下一代視覺(jué)處理技術(shù)

- Inuitive? 和業(yè)界領(lǐng)先的提供片上網(wǎng)絡(luò)(NoC)互連和IP部署軟件以加快系統(tǒng)級(jí)芯片(SoC)創(chuàng)建的系統(tǒng)IP供應(yīng)商 Arteris? Inc.今天宣布,Inuitive 已為其下一代計(jì)算機(jī)視覺(jué)平臺(tái)部署了 Arteris FlexNoC? 互連 IP。該技術(shù)解決了連接和時(shí)序收斂的挑戰(zhàn),可以實(shí)現(xiàn)先進(jìn)的下一代前沿視覺(jué)處理器所需的激進(jìn)性能目標(biāo)。這些先進(jìn)的 SoC 將擴(kuò)展多核視覺(jué)處理并增強(qiáng)高質(zhì)量的深度傳感。這些芯片將部署在 3D 深度成像、物體識(shí)別和跟蹤,以及其他使用計(jì)算機(jī)視覺(jué)算法的各種應(yīng)用中,比如增強(qiáng)現(xiàn)實(shí)、虛

- 關(guān)鍵字: Arteris IP 視覺(jué)處理器

燦芯半導(dǎo)體推出兩項(xiàng)創(chuàng)新技術(shù)用于DDR物理層

- 一站式定制芯片及IP供應(yīng)商——燦芯半導(dǎo)體日前宣布推出用于高速DDR物理層中的Zero-Latency (零延遲)和True-Adaptive(真自適應(yīng))兩項(xiàng)技術(shù)。這兩項(xiàng)技術(shù)已經(jīng)開(kāi)始在12/14 FinFET, 22/28nm的DDR4/LPDDR4,4x高性能物理層IP上進(jìn)行部署,將為客戶帶來(lái)更高效、更穩(wěn)定的全新體驗(yàn)。 Zero-Latency (零延遲) 技術(shù)在讀數(shù)據(jù)通路上,采用了兩種可選的、獨(dú)特的采樣方式進(jìn)行數(shù)據(jù)轉(zhuǎn)換,而不像其他DDR物理層供貨商采用FIFO進(jìn)行跨時(shí)鐘域轉(zhuǎn)換,此技術(shù)將延遲降低

- 關(guān)鍵字: 燦芯 DDR IP

ucie ip介紹

您好,目前還沒(méi)有人創(chuàng)建詞條ucie ip!

歡迎您創(chuàng)建該詞條,闡述對(duì)ucie ip的理解,并與今后在此搜索ucie ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)ucie ip的理解,并與今后在此搜索ucie ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司