- 2011年9月6日-萊迪思半導體公司(NASDAQ: LSCC)2011年9月6日宣布MachXO2 PLD系列的2.5mmx2.5mm 25球型晶圓級芯片尺寸封裝(WLCSP)的樣片現(xiàn)已發(fā)運。目前MachXO2器件結(jié)合了超小封裝尺寸——至今在PLD市場還未被超越——具有行業(yè)最低功耗和最豐富功能的低密度PLD。使用低功耗65nm工藝的嵌入式閃存技術(shù)構(gòu)建,MachXO2系列增加了3倍的邏輯密度,提高了10倍的嵌入式存儲器,并且與前代產(chǎn)品相比減少了100倍的靜態(tài)功耗。MachXO2器件具有業(yè)界最穩(wěn)定的PLD功

- 關(guān)鍵字:

萊迪思 半導體 MachXO2

- 萊迪思半導體公司日前宣布MachXO2 PLD系列的2.5mmx2.5mm 25球型晶圓級芯片尺寸封裝(WLCSP)的樣片現(xiàn)已發(fā)運。目前MachXO2器件結(jié)合了超小封裝尺寸——至今在PLD市場還未被超越——具有行業(yè)最低功耗和最豐富功能的低密度PLD。使用低功耗65nm工藝的嵌入式閃存技術(shù)構(gòu)建,MachXO2系列增加了3倍的邏輯密度,提高了10倍的嵌入式存儲器,并且與前代產(chǎn)品相比減少了100倍的靜態(tài)功耗。

- 關(guān)鍵字:

萊迪思 PLD

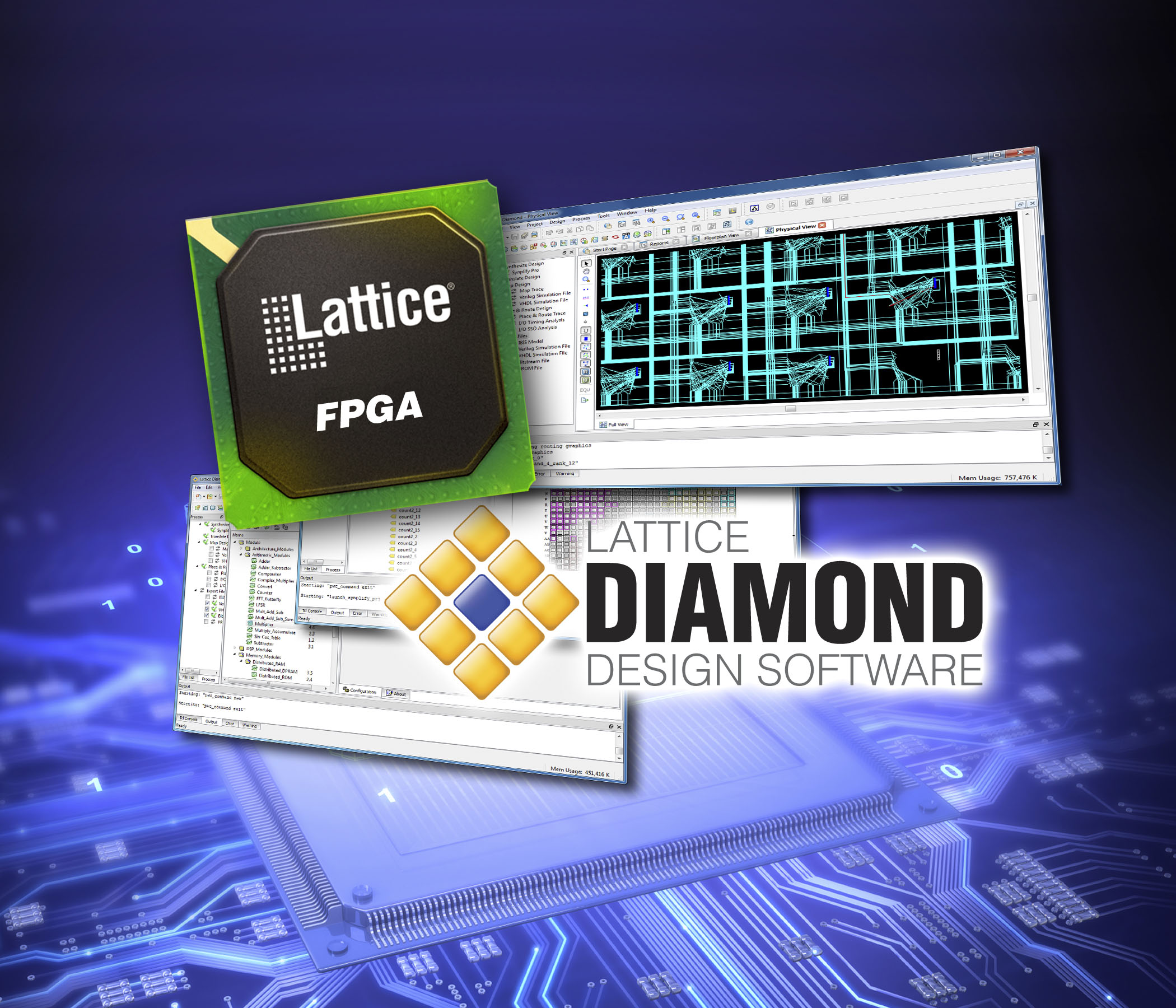

- 萊迪思半導體公司(NASDAQ: LSCC)宣布推出Lattice Diamond 設計軟件,針對萊迪思FPGA產(chǎn)品的旗艦設計環(huán)境。Lattice Diamond 1.3軟件的用戶將受益于主要的新功能,包括時鐘抖動分析。現(xiàn)在Lattice Diamond 1.3軟件還集成了萊迪思的PAC- Designer 6.1混合信號設計工具,為萊迪思的可編程混合信號Platform Manager 器件提供設計支持。

- 關(guān)鍵字:

萊迪思 Lattice Diamond

- 萊迪思半導體公司日前宣布LatticeECP3TMFPGA系列符合PCI Express 2.0在2.5Gbps的規(guī)范。針對最近PCI – SIG研討會上涉及的1-通道和 4-通道配置,LatticeECP3 FPGA和其PCI Express(PCIe)IP核通過了符合PCI - SIGPCIe 2.0規(guī)范和互操作性的測試,確保萊迪思的解決方案與現(xiàn)有的支持系統(tǒng)的PCIe 2.0具有互操作性。

- 關(guān)鍵字:

萊迪思 FPGA

- 萊迪思半導體公司和FLEXIBILIS Oy日前宣布了即可獲取Flexibilis以太網(wǎng)交換(FES)IP核。三速(10Mbps/100Mbps/1Gbps)FES IP核工作在以太網(wǎng)第2層,每個端口具有Gigabit的轉(zhuǎn)換能力。支持Gigabit光纖和Gigabit雙絞線銅以太網(wǎng)接口。支持的服務質(zhì)量高達每端口四個隊列。這些以太網(wǎng)交換IP核有五個版本,根據(jù)端口數(shù)和功能而不同:

- 關(guān)鍵字:

萊迪思 FPGA

- 萊迪思半導體公司(NASDAQ: LSCC)和器件編程工具的領(lǐng)先供應商System General今天宣布推出了自動和手動編程系統(tǒng),現(xiàn)已全面支持MachXO2? PLD系列的第一個成員,1200 LUT的LCMXO2-1200。兩家公司之間的合作確保正在進入新的電子系統(tǒng)的生產(chǎn)階段的用戶使用System General編程設備,將不會發(fā)生開發(fā)延遲,或產(chǎn)生額外的NRE成本用以支持MachXO2 PLD。

- 關(guān)鍵字:

萊迪思 PLD編程

- 萊迪思半導體公司今日宣布即可獲取新的29美元的MachXO2? Pico開發(fā)套件,可用于低功耗,空間受限的消費電子設計的樣機研制。采用嵌入式閃存技術(shù)的低功耗65納米工藝的MachXO2器件為低密度PLD設計人員提供了在單個器件中前所未有的低成本,低功耗和高系統(tǒng)集成的特性。這些器件是低功耗應用的理想選擇,如智能手機、移動計算、GPS設備和數(shù)碼相機,以及在終端市場的控制PLD的應用,如電信基礎設施、計算,高端產(chǎn)業(yè)和高端醫(yī)療設備。

- 關(guān)鍵字:

萊迪思 開發(fā)套件

- 萊迪思半導體公司今日宣布全面支持使用LatticeXP2TM FPGA的Aptina的高速串行像素接口(HiSPi)。LatticeXP2 HiSPi橋參考設計實現(xiàn)了任意帶有傳統(tǒng)CMOS并行總線的圖像信號處理器(ISP)與Aptina HiSPi CMOS傳感器的連接。HiSPi橋解決方案是使用更高分辨率和更高的幀速率的CMOS傳感器的理想選擇,如安防攝像、汽車應用、高端消費攝像和其他攝像應用等。

- 關(guān)鍵字:

萊迪思 圖像信號處理器

- 萊迪思半導體公司和Helion Technology今日宣布一系列適用于LatticeECP3 FPGA系列的壓縮和加密的IP核現(xiàn)已上市。該系列具有有效載荷壓縮系統(tǒng)核,提高了有限信道帶寬的利用率,因此非常適合微波回程應用、寬帶無線接入適用于802.16e(WiMAX)以及潛在的其他多鏈路多輸入-多輸出(MIMO)應用中的使用。在LatticeECP3器件中,IP核可以從500Mbps無縫擴展至超過3Gbps,并可用于典型的網(wǎng)絡應用中的第2層或第3層。IP核采用了非常強大和成熟的LZRW無損壓縮算法,它

- 關(guān)鍵字:

萊迪思 FPGA

- 萊迪思半導體公司(NASDAQ: LSCC)今天宣布,其屢獲殊榮的Platform Manager?系列產(chǎn)品完全合格并進入量產(chǎn)階段。與此量產(chǎn)信息發(fā)布相配合的是更新的PAC-Designer? 6.0.1設計軟件,它使模擬和電路板設計師將電路板的電源管理和數(shù)字板的管理功能集成至Platform Manager器件系列。此外,現(xiàn)在即可獲取另外11個參考設計(包括風扇控制器,邊界掃描端口連接器和GPIO擴展器),這些都為使用Platform Manager產(chǎn)品而進行了專門的測試。

- 關(guān)鍵字:

萊迪思 電路板

- 萊迪思半導體公司今天宣布推出印刷版的書“Power 2 You”, 針對電路板的電源管理功能,為設計人員提供150頁的技術(shù)細節(jié)和設計考慮。作者是Srirama(“Shyam”) Chandra,他是電源管理領(lǐng)域被認可的專家,發(fā)表了多篇有關(guān)電源管理的文章。

- 關(guān)鍵字:

萊迪思 電源管理

- 萊迪思半導體公司今天宣布推出其新的MachXO2? PLD系列,為低密度PLD的設計人員提供了在單個器件中前所未有的低成本,低功耗和高系統(tǒng)集成。嵌入式閃存技術(shù)采用了低功耗65納米工藝,與MachXO? PLD系列相比,MachXO2系列提供了3倍的邏輯密度、10倍的嵌入式存儲器、降低了100倍以上的靜態(tài)功耗并減少了高達30%的成本。

- 關(guān)鍵字:

萊迪思 PLD

- 萊迪思半導體公司今日發(fā)布了ispLEVER? Classic設計工具套件1.4版。ispLEVER Classic設計軟件已經(jīng)升級,添加了帶有HDL Analyst功能集的Synopsys Synplify Pro,以及改進的ispMACH? 4000ZE CPLD Fitter,具有更好的功耗優(yōu)化功能。

Synplify Pro HDL Analyst為設計師們提供了快速直觀地實現(xiàn)高階寄存器傳輸級(RTL)Verilog或VHDL的方法。設計師可以在圖和源代碼之間進行交叉查詢,

- 關(guān)鍵字:

萊迪思 設計工具套件 ispLEVER

- 引言

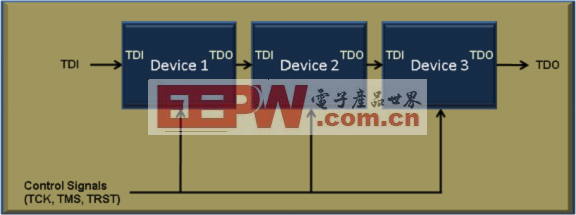

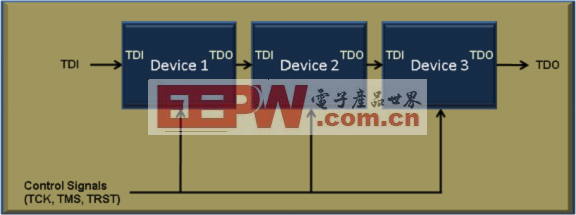

隨著JTAG標準IEEE1149.1的定型,及隨后開始在集成電路Intel 80486中采用,邊界掃描測試已被廣泛應用于測試印刷電路板的連接,以及在集成電路內(nèi)進行測試。邊界掃描測試受到設計人員的歡迎,因為它能夠在線測試,而無需昂貴的釘床在線測試設備。然而,在大的電路板上,邊界掃描鏈路很長,電路板設計人員面臨著多種挑戰(zhàn),諸如故障檢測和隔離、測試時間、物理布線,同時還要管理偏移,電壓轉(zhuǎn)換和滿足各種特殊需要。傳統(tǒng)上使用ASSP來應對這些挑戰(zhàn),然而基于ASSP的解決方案更為昂貴,有固定的電平和一些

- 關(guān)鍵字:

萊迪思 PLD

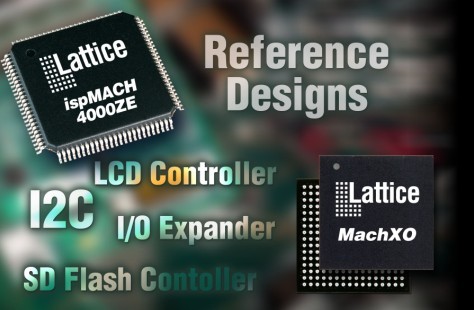

- 萊迪思半導體公司今天宣布已經(jīng)推出了針對MachXO™和ispMACH® 4000ZE PLD而優(yōu)化的超過90個參考設計。參考設計能夠幫助設計人員快速和高效地進行設計,并能有效使用這些常用功能,諸如通用I/O擴展、I2C總線主/從、LCD控制器、SD閃存控制器,以及其他接口,這些功能廣泛地用于各種市場,包括消費、通訊、計算機,工業(yè)和醫(yī)療等。這些參考設計與完整的文檔和設計源代碼結(jié)合在一起完全可以適應客戶的需求,使設計人員縮短設計時間,提高工作效率并加快產(chǎn)品的上市。

&ldqu

- 關(guān)鍵字:

萊迪思 參考設計 PLD

萊迪思介紹

您好,目前還沒有人創(chuàng)建詞條萊迪思!

歡迎您創(chuàng)建該詞條,闡述對萊迪思的理解,并與今后在此搜索萊迪思的朋友們分享。

創(chuàng)建詞條

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473