一種基于DSP平臺的快速H.264編碼算法的設計

視頻壓縮編碼標準H.264/AVC是由ISO/IEC和ITU-T組成的聯合視頻專家組(JVT)制定的,他引進了一系列先進的視頻編碼技術,如4×4整數變換、空域內的幀內預測,多參考幀與多種大小塊的幀間預測技術等,標準一經推出,就以其高效的壓縮性能和友好的網絡特性受到業界的廣泛推崇。特別是在2004年7月JVT組織做了重要的保真度范圍擴展的補充后,更加擴大了標準的應用范圍,但同時巨大的運算量卻成為其廣泛應用的瓶頸。考慮到H.264協議實現的復雜度,本文的思路是:一方面提高硬件處理速度和能力,采用TI公司最新的數字媒體處理器Davinci TMS320DM6446 DSP芯片作為H.264編碼器實現的硬件平臺,另一方面提高算法效率。最后提出一個基于這個芯片的嵌入式H.264編碼器的設計方案。

本文引用地址:http://www.czjhyjcfj.com/article/84083.htm1 硬件平臺

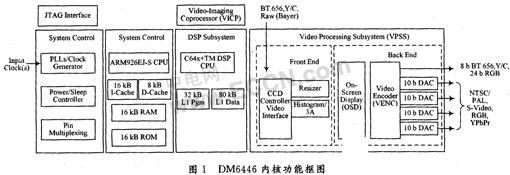

1.1 Davinci DM6446芯片介紹

DM6446采用DSP+ARM的雙內核結構(內核圖見圖1),其中的DSP芯片的CPU時鐘頻率可達594 MHz,ARM的引入可以釋放DSP在控制方面的部分功能,使DSP專門進行數據處理的工作。芯片采用增強型的哈佛結構總線,其CPU內部有2個數據通道,8個32 b的功能單元,2個通用寄存器組(A和B),可同時執行8條32 b長指令。如果能充分利用這8個功能單元,總字長為256 b的指令包同時分配到8個并行處理單元,在完全流水的情況下,該芯片的指令吞吐量將達到594×8=4 752 MIPS。處理器具有雙16 b擴充功能,芯片能在一個周期內完成雙16 b的乘法、加減法、比較、移位等操作。該芯片內部支持兩級Cache,其中第一級32 kB的程序緩存器L1P,80 kB的數據緩存器L1D,而第二級的Cache大小是可配置的64 kB,芯片自動完成這兩級Cache之間數據一致性的維護。有了這兩級Cache的支持將使CPU的執行速度大大加快。

Davinci DM6446具有專用的視頻圖像處理子系統。視頻處理子系統包括1個視頻前端和1個視頻末端,視頻前端的輸入接口用于接受外部傳感器或視頻譯碼器輸出的BT.656等圖像輸入信息;視頻末端輸出接口輸出圖像,實現圖像本地重現。

視頻前端輸入(VPFE)接口由1個CCD控制器(CCDC),1個預處理器,柱狀模塊,自動曝光/白平衡/聚焦模塊(H3A)和寄存器組成。CCD控制器可以與視頻解碼器CMOS傳感器或電荷耦合裝置連接。預處理器是一個實時的圖形處理器。

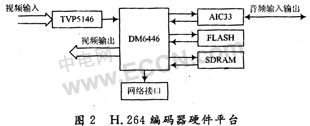

1.2 H.264編碼器硬件平臺

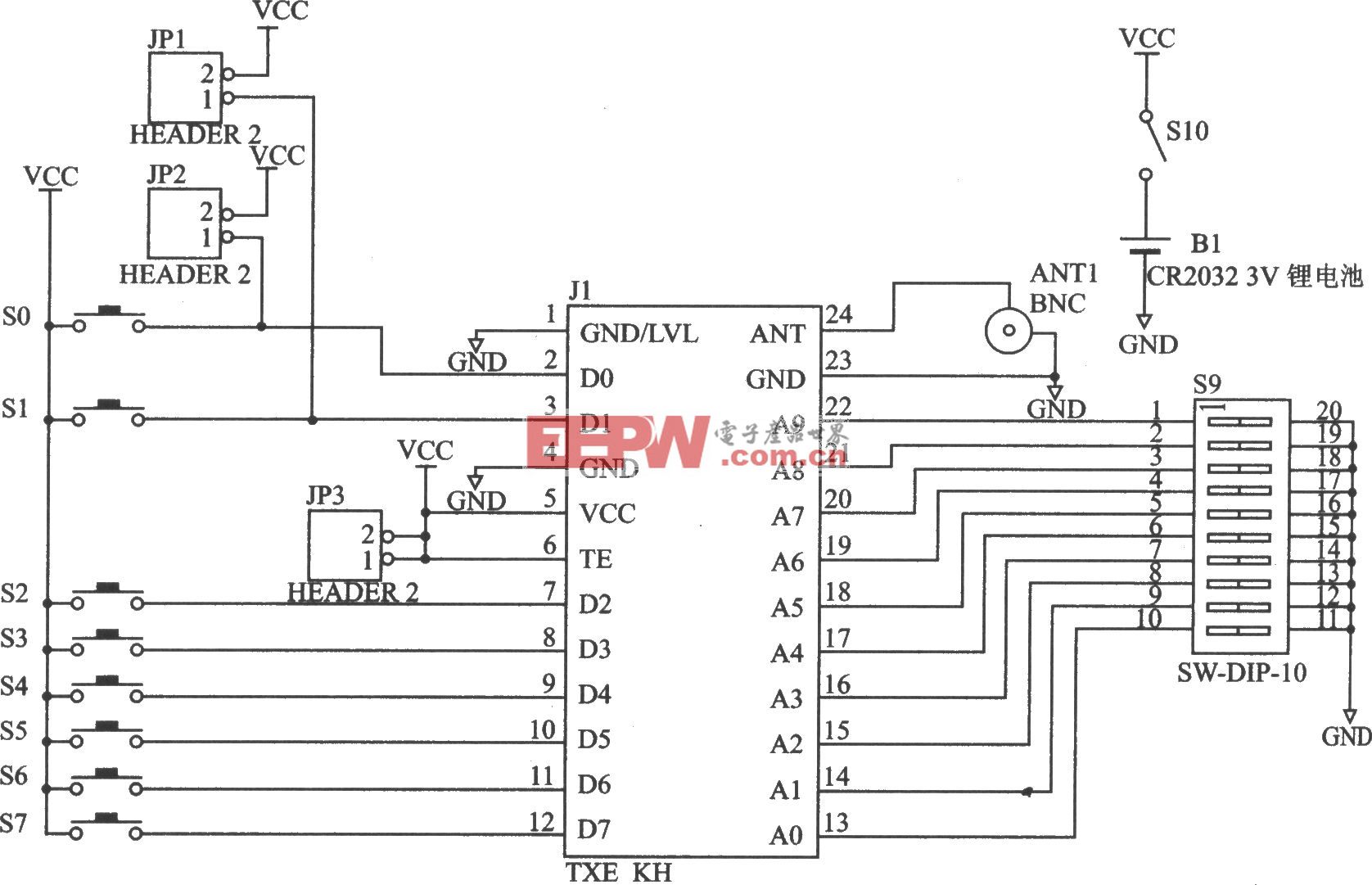

本系統的平臺核心處理芯片為Davinci DM6446,如圖2所示,片外RAM選取兩片DDR并聯成32位的數據寬度,空間為256 MB。模擬視頻信號在“VIDEO IN”引入后經過解碼芯片TVP5146變換為數字信號后輸入TMS320DM6446芯片中進行處理,H.264編碼處理后的碼流可以通過視頻末端輸出保存在本地硬盤上,以方便調試檢查。或者可以通過10/100 M以太網物理層接口輸出,進行網絡傳輸。同時,本地的重構圖像可以通過TMS320DM6446芯片內部OSD模塊和編碼模塊D/A變換后直接顯示輸出。

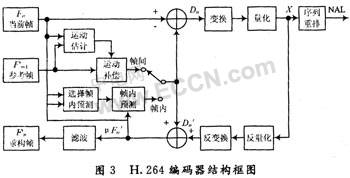

2 H.264編碼器結構與編碼流程

2.1 H.264編碼器結構

如圖3所示輸入的圖像以宏塊為單位進入編碼器中,根據圖像變化的快慢選擇幀內或幀間預測編碼。如果選擇幀內預測編碼,首先判斷當前待編碼塊中是否包含很多的細節,再決定是否要把幀進行再分割。接著以重建幀μF′n中的塊為參考,結合當前塊周圍塊的預測模式,選擇當前塊的最佳預測模式。最后由重建幀μF′n中相應塊和當前塊選定的預測模式得到當前塊的預測值。按照上述方法,對圖像中的每一宏塊作出幀內預測,進而得到一幀圖像的預測值P。如果選擇幀間預測編碼,當前輸入幀Fn和前一幀(參考幀)Fn-1被送到運動估計器(ME),通過塊搜索,匹配可以得到當前幀中的各宏塊相對于參考幀中對應宏塊的偏移量,也就是常說的運動矢量。接著,參考幀Fn-1和剛得到的運動矢量MV被送到運動補償器(MC),通過計算得到幀間預測值P;當前幀Fn和幀預測值P相減,得到殘差Dn,經過變換,量化后產生一組量化后的變換系數X,再經過熵編碼,與解碼所需的一些邊信息(如預測模式量化參數,運動矢量等)一起組成一個壓縮后的碼流,經NAL(網絡自適應層)供傳輸和存儲。

評論