ARM存儲器之:高速緩沖存儲器Cache

15.3高速緩沖存儲器Cache

當第一代RISC微處理器剛出現時,標準存儲器元件的速度比當時微處理器的速度快。很快,半導體工藝技術的進展被用來提高微處理器的速度。標準DRAM部件雖然也快了一些,但其發展的主要精力則放在提高存儲容量上。

1980年,典型DRAM部件的容量為4KB。1981年和1982年開發出了16KB芯片。這些部件的隨機訪問速率為3MHz或4MHz,局部訪問(頁模式)時速率大約快1倍。當時的微處理器每秒需要訪問存儲器2M次。

到2000年,DRAM部件每片的容量到達256Mbit,隨機訪問速率在30MHz左右。微處理器每秒需要訪問存儲器幾百兆次。如果處理器速率遠高于存儲器,那么只能借助Cache才能滿足其全部性能。

Cache存儲器是一個容量小但存取速度非常快的存儲器,它保存最近用到的存儲器數據拷貝。對于程序員來說,Cache是透明的。它自動決定保存哪些數據、覆蓋哪些數據。現在Cache通常與處理器在同一芯片上實現。Cache能夠發揮作用是因為程序具有局部性特性。所謂局部性就是指,在任何特定的時間,微處理器趨于對相同區域的數據(如堆棧)多次執行相同的指令(如循環)。

Cache經常與寫緩存器(writebuffer)一起使用。寫緩存器是一個非常小的先進先出(FIFO)存儲器,位于處理器核與主存之間。使用寫緩存的目的是,將處理器核和Cache從較慢的主存寫操作中解脫出來。當CPU向主存儲器做寫入操作時,它先將數據寫入到寫緩存區中,由于寫緩存器的速度很高,這種寫入操作的速度也將很高。寫緩存區在CPU空閑時,以較低的速度將數據寫入到主存儲器中相應的位置。

通過引入Cache和寫緩存區,存儲系統的性能得到了很大的提高,但同時也帶來了一些問題。比如,由于數據將存在于系統中的不同的物理位置,可能造成數據的不一致性;由于寫緩存區的優化作用,可能有些寫操作的執行順序不是用戶期望的順序,從而造成操作錯誤。

15.3.1Cache的分類

Cache有多種構造方法。在最高層次,微處理器可以采用下面兩種組織中的一組。

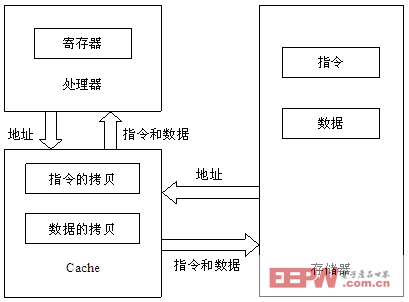

(1)統一Cache。指令和數據用同一個Cache。結構如圖15.8所示。

圖15.8統一的指令Cache和數據Cache

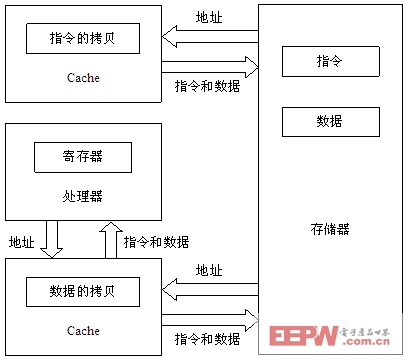

(2)指令和數據分開的Cache。有時這種組織方式也被稱為改進的哈佛結構。

圖15.9顯示了這種組織方式。

這兩種組織方式各有優缺點。統一Cache能夠根據當前程序的需要自動調整指令在Cache存儲器的比例,比固定劃分的有更好的性能。另一方面,分開的Cache使Load/Store指令能夠單周期執行。

15.3.2Cache性能的衡量

只有當所需要的Cache存儲器內容已經在Cache時,微處理器才能以高時鐘速率工作。因此,系統的總體性能就可以用存儲器訪問中命中Cache的比例來衡量。當要訪問的內容在Cache時稱為命中(hit),而要訪問的內容不在Cache時稱為未命中(miss)。在給定時間間隔內,Cache命中的次數與總的存儲器請求次數的比值被稱為命中率。

圖15.9指令Cache和數據分開的Cache

命中率用下面的公式進行計算:

命中率=(Cache命中次數÷存儲器請求次數)×100%

未命中率與命中率形式相似,即在給定時間間隔內,Cache未命中的總次數除以總的存儲器請求次數所得的百分比。未命中率與命中率之和等于100。

目前設計良好的處理器,Cache的未命中率只有百分之幾。未命中率依賴多個Cache參數,包括Cache大小和組織。

存儲器相關文章:存儲器原理

評論