芯片巨頭們已著手研發(fā)下一代CFET技術

外媒 eNewsEurope 報道,英特爾 (Intel) 和臺積電將在國際電子元件會議 (IEDM) 公布垂直堆疊式 (CFET) 場效晶體管進展,使 CFET 成為十年內最可能接替閘極全環(huán)電晶 (GAA ) 晶體管的下一代先進制程。

本文引用地址:http://www.czjhyjcfj.com/article/202310/451309.htm英特爾的 GAA 設計堆疊式 CFET 晶體管架構是在 imec 的幫助下開發(fā)的,設計旨在增加晶體管密度,通過將 n 和 p 兩種 MOS 器件相互堆疊在一起,并允許堆疊 8 個納米片(RibbonFET 使用的 4 個納米片的兩倍)來實現(xiàn)更高的密度。目前,英特爾正在研究兩種類型的 CFET,包括單片式和順序式,但尚未確定最終采用哪一種,或者是否還會有其他類型的設計出現(xiàn),未來應該會有更多細節(jié)信息公布。

此前在 2021 年的「英特爾加速創(chuàng)新:制程工藝和封裝技術線上發(fā)布會」上,英特爾已經確認了 RibbonFET 將成歷史,在其 20A 工藝上,將引入采用 Gate All Around(GAA)設計的 RibbonFET 晶體管架構,以取代自 2011 年推出的 FinFET 晶體管架構。新技術將加快了晶體管開關速度,同時實現(xiàn)與多鰭結構相同的驅動電流,但占用的空間更小。

雖然,大多數(shù)早期研究以學術界為主,但英特爾和臺積電等半導體企業(yè)現(xiàn)在已經開始這一領域的研發(fā),借此積極探索這種下一代先進晶體管技術。

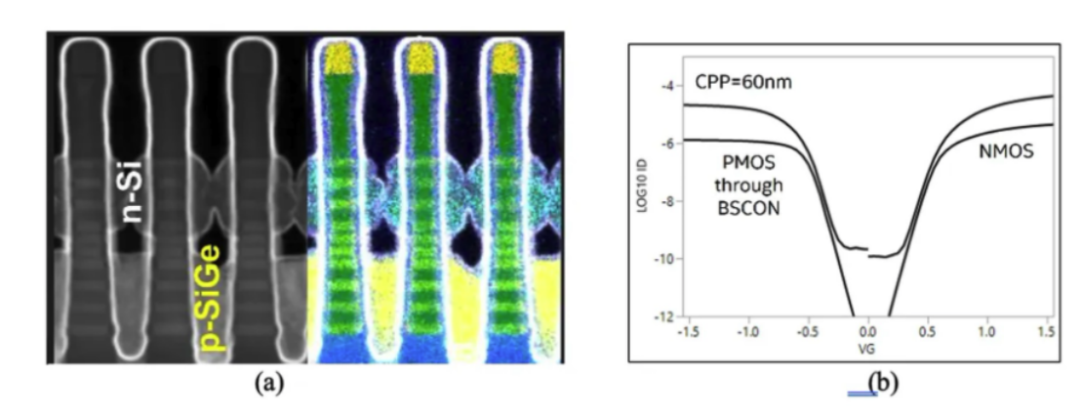

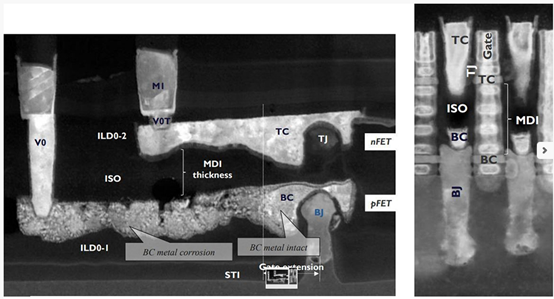

英特爾表示,研究員建構一個單片 3D CFET,含三個 n-FET 納米片,層疊在三個 p-FET 納米片上,保持 30 納米垂直間隙,取名為采用電源通孔和直接背面元件觸點 60 納米閘極間距堆疊式 CMOS 逆變器示范,描述 60 納米閘極間距利用 CFET 功能逆變器測試電路。采垂直分層雙電源漏外延和雙金屬閘極堆疊,結合 PowerVia 背后供電。

為了不被對手超越,臺積電也會展示如何達成 CFET。此為客制邏輯芯片,有 48 納米柵極間距,專注放在 p 型晶體管上的分層 n 型納米片晶體管,擁有跨越六個等級的卓越開關電流比。

臺積電 CFET 晶體管已證明耐用性超過 90%,且成功通過測試。雖然臺積電承認需要研究更多,才能充分利用 CFET 技術,但是實現(xiàn) CFET 晶體管技術的關鍵。CFET 明顯轉變晶體管設計,允許垂直堆疊兩個晶體管安裝至一個晶體管面積內,增加晶體管密度,且不僅為提高空間使用提供解決方案,還促進更精簡 CMOS 邏輯電路布局,有利提高設計效率。

CFET 既有結構可能會減少寄生效應,逐漸提高性能和功率效率。結合適應性設計與背面供電等創(chuàng)新,可簡化制程復雜性,使 CFET 成為晶體管領域愿景。英特爾和臺積電的努力,也突顯 CFET 技術對半導體產業(yè)未來的重要性。

復旦大學研發(fā)出異質 CFET 技術

復旦大學研究團隊:周鵬教授、包文中研究員及萬景研究員,創(chuàng)新地提出了硅基二維異質集成疊層晶體管。該技術將新型二維原子晶體引入傳統(tǒng)的硅基芯片制造流程,繞過 EUV 光刻工藝,實現(xiàn)了晶圓級異質 CFET 技術。

該團隊利用硅基集成電路的成熟后端工藝,將二硫化鉬 (MoS2) 三維堆疊在傳統(tǒng)的硅基芯片上,形成 p 型硅-n 型二硫化鉬的異質互補 CFET 結構。結果證明,在相同的工藝節(jié)點下實現(xiàn)了器件集成密度翻倍,并獲得了卓越的電學性能。

簡單來說,就是該團隊研發(fā)出的異質 CFET 技術,是設計了一種晶圓級硅基二維互補疊層晶體管,不需要用到 EUV,也可以實現(xiàn)晶體管密度翻倍。

隨著芯片工藝制程不斷進步,就需要尺寸更小、功能更強大的晶體管,同時,會讓制程微縮到一定程度,原本的晶體管技術就會出現(xiàn)靜電、漏電問題。因此,晶體管技術也隨著工藝迭代加快升級,而升級的重點在于提升靜電性能、控制漏電流。

比如,22nm 工藝之后,F(xiàn)inFET 取代 MOSFE 工藝,3nm 工藝時代,GAAFET 取代 FinFET 工藝,再先進的工藝(比如 2nm 以下),CFET 將取代 GAAFET 工藝。因此,CFET 是 GAAFET 工藝的迭代技術,也稱之為全硅基 CFET 技術。

這對于國內自主發(fā)展新型集成電路技術具有重要意義。畢竟,在中企無法獲得先進的 EUV 光刻機下,該技術給予了另一種可行性研究方向。如果一旦成功應用,那么將會繞過 EUV 光刻機的問題,制造出更先進的芯片。

以及 CFET 屬于下一代晶體管技術,是未來發(fā)展的重點,該技術的研發(fā)有利于我們取得先機。特別是在關鍵技術專利方面,先取得更多的研究成果與專利,對于后期芯片制程的發(fā)展是更有利的。

評論