Verilog HDL基礎(chǔ)之:賦值語句和塊語句

非阻塞賦值和阻塞賦值

在Verilog HDL語言中,信號(hào)有兩種賦值方式:非阻塞(Non_Blocking)賦值方式和阻塞(Blocking)賦值方式。

(1)非阻塞賦值方式。

典型語句:b = a;

① 塊結(jié)束后才完成賦值操作。

② b的值并不是立刻就改變的。

③ 這是一種比較常用的賦值方法,特別在編寫可綜合模塊時(shí)。

(2)阻塞賦值方式。

典型語句:b = a;

① 賦值語句執(zhí)行完后,塊才結(jié)束。

② b的值在賦值語句執(zhí)行完后立刻就改變。

③ 可能會(huì)產(chǎn)生意想不到的結(jié)果。

非阻塞賦值方式和阻塞賦值方式的區(qū)別常給設(shè)計(jì)人員帶來問題。問題主要是給“always”塊內(nèi)的reg型信號(hào)的賦值方式不易把握。到目前為止,前面所舉的例子中的“always”模塊內(nèi)的reg型信號(hào)都是采用下面的這種賦值方式:

b = a;

這種方式的賦值并不是馬上執(zhí)行的,也就是說“always”塊內(nèi)的下一條語句執(zhí)行后,b并不等于a,而是保持原來的值。“always”塊結(jié)束后,才進(jìn)行賦值。而另一種賦值方式阻塞賦值方式,如下所示:

b = a;

這種賦值方式是馬上執(zhí)行的,也就是說執(zhí)行下一條語句時(shí),b已等于a。盡管這種方式看起來很直觀,但是可能引起麻煩。下面舉例說明。

例1:非阻塞賦值。

always @( posedge clk ) begin

b=a;

c=b;

end

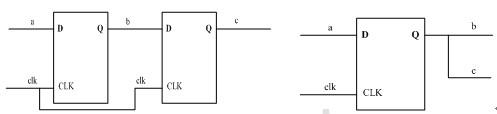

例1中的“always”塊中用了非阻塞賦值方式,定義了兩個(gè)reg型信號(hào)b和c。clk信號(hào)的上升沿到來時(shí),b就等于a,c就等于b,這里應(yīng)該用到了兩個(gè)觸發(fā)器。需要注意的是賦值是在“always”塊結(jié)束后執(zhí)行的,c應(yīng)為原來b的值。這個(gè)“always”塊實(shí)際描述的電路功能如圖1所示。

例2:阻塞型賦值。

always @(posedge clk) begin

b=a;

c=b;

end

例2中的“always”塊用了阻塞賦值方式。clk信號(hào)的上升沿到來時(shí),將發(fā)生如下的變化:b馬上取a的值,c馬上取b的值(即等于a)。綜合的電路如圖2所示。

圖1 非阻塞賦值綜合電路 圖2 阻塞賦值綜合電路

它只用了一個(gè)觸發(fā)器來寄存a的值,并同時(shí)輸出給b和c。這不是設(shè)計(jì)者的初衷,如果采用例3.5所示的非阻塞賦值方式就可以避免這種錯(cuò)誤。

塊語句

塊語句通常用來將兩條或多條語句組合在一起,使其在格式上看更像一條語句。塊語句有兩種:一種是begin_end語句,通常用來標(biāo)識(shí)順序執(zhí)行的語句,用它來標(biāo)識(shí)的塊稱為順序塊;另一種是fork_join語句,通常用來標(biāo)識(shí)并行執(zhí)行的語句,用它來標(biāo)識(shí)的塊稱為并行塊。下面進(jìn)行詳細(xì)的介紹。

1.順序塊

順序塊有以下特點(diǎn)。

(1)塊內(nèi)的語句是按順序執(zhí)行的,即只有上面一條語句執(zhí)行完后下面的語句才能執(zhí)行。

(2)每條語句的延遲時(shí)間是相對(duì)于前一條語句的仿真時(shí)間而言的。

(3)直到最后一條語句執(zhí)行完,程序流程控制才跳出該語句塊。

順序塊的格式如下:

begin

語句1;

語句2;

......

語句n;

end

或者:

begin:塊名

塊內(nèi)聲明語句

語句1;

語句2;

......

語句n;

end

其中:

(1)塊名即該塊的名字,是一個(gè)標(biāo)識(shí)符,其作用后面再詳細(xì)介紹。

(2)塊內(nèi)聲明語句可以是參數(shù)聲明語句,reg型變量聲明語句,integer型變量聲明語句或者real型變量聲明語句。

下面舉例說明。

例3:順序塊。

begin

areg = breg;

creg = areg; //creg的值為breg的值

end

從該例可以看出,第一條賦值語句先執(zhí)行,areg的值更新為breg的值。然后程序流程控制轉(zhuǎn)到第二條賦值語句,creg的值更新為areg的值。因?yàn)檫@兩條賦值語句之間沒有任何延遲時(shí)間,creg的值實(shí)為breg的值。當(dāng)然可以在順序塊里延遲控制時(shí)間來分開兩個(gè)賦值語句的執(zhí)行時(shí)間,如例4所示。

例4:加延時(shí)順序塊。

begin

areg = breg;

#10 creg = areg; //在兩條賦值語句間延遲10個(gè)時(shí)間單位

end

2.并行塊

并行塊有以下4個(gè)特點(diǎn)。

(1)塊內(nèi)語句是同時(shí)執(zhí)行的,即程序流程控制一進(jìn)入該并行塊,塊內(nèi)語句則開始同時(shí)并行地執(zhí)行。

(2)塊內(nèi)每條語句的延遲時(shí)間是相對(duì)于程序流程控制進(jìn)入到塊內(nèi)時(shí)的仿真時(shí)間的。

(3)延遲時(shí)間是用來給賦值語句提供執(zhí)行時(shí)序的。

(4)當(dāng)按時(shí)間時(shí)序排序在最后的語句執(zhí)行完后或一個(gè)disable語句執(zhí)行時(shí),程序流程控制跳出該程序塊。

并行塊的格式如下:

fork

語句1;

語句2;

.......

語句n;

join

或者:

fork:塊名

塊內(nèi)聲明語句

語句1;

語句2;

......

語句n;

join

其中:

(1)塊名即標(biāo)識(shí)該塊的一個(gè)名字,相當(dāng)于一個(gè)標(biāo)識(shí)符。

(2)塊內(nèi)說明語句可以是參數(shù)說明語句、reg型變量聲明語句、integer型變量聲明語句、real型變量聲明語句、ime型變量聲明語句或者事件(event)說明語句。

下面舉例說明。

例5:并行塊1。

fork

#50 r = h35; //在絕對(duì)時(shí)間50單位后,r被賦值

#100 r = hE2; //在絕對(duì)時(shí)間100單位后(非絕對(duì)時(shí)間150),r再次被賦值

#150 r = h00;

#200 r = hF7;

#250 -> end_wave; //在絕對(duì)時(shí)間250單位后,觸發(fā)事件end_wave

join

在這個(gè)例子中用并行塊來替代前面例子中的順序塊來產(chǎn)生波形,用這兩種方法生成的波形是一樣的。

3.塊名

在Verilog HDL語言中,可以給每一個(gè)塊取名字,只需將名字加在關(guān)鍵詞begin或fork后面即可,這樣做的原因有以下幾點(diǎn)。

(1)這樣可以在塊內(nèi)定義局部變量,即只在塊內(nèi)使用的變量。

(2)這樣可以允許塊被其他語句調(diào)用,如被disable語句調(diào)用。

(3)在Verilog語言里,所有的變量都是靜態(tài)的,即所有的變量都只有一個(gè)惟一的存儲(chǔ)地址,因此進(jìn)入或跳出塊并不影響存儲(chǔ)在變量內(nèi)的值。

基于以上原因,塊名就提供了一個(gè)在任何仿真時(shí)刻確認(rèn)變量值的方法。需要注意的是,塊名和變量名一樣,都不能是關(guān)鍵詞。

4.起始時(shí)間和結(jié)束時(shí)間

在并行塊和順序塊中都有一個(gè)起始時(shí)間和結(jié)束時(shí)間的概念。對(duì)于順序塊,起始時(shí)間就是第一條語句開始被執(zhí)行的時(shí)間,結(jié)束時(shí)間就是最后一條語句執(zhí)行完的時(shí)間。而對(duì)于并行塊來說,起始時(shí)間對(duì)于塊內(nèi)所有的語句是相同的,即程序流程控制進(jìn)入該塊的時(shí)間,其結(jié)束時(shí)間是按時(shí)間排序在最后的語句執(zhí)行完的時(shí)間。

當(dāng)一個(gè)塊嵌入另一個(gè)塊時(shí),塊的起始時(shí)間和結(jié)束時(shí)間是很重要的。跟在塊后面的語句只有在該塊的結(jié)束時(shí)間到了才能開始執(zhí)行,也就是說,只有該塊完全執(zhí)行完后,后面的語句才可以執(zhí)行。

在fork_join塊內(nèi),各條語句不必按順序給出,因此在并行塊里,各條語句在前還是在后是無關(guān)緊要的,如下所示。

例6:并行塊2。

fork

#250 -> end_wave; //按下面幾條語句順序執(zhí)行結(jié)果和例[6]的執(zhí)行結(jié)果一樣

#200 r = hF7;

#150 r = h00;

#100 r = hE2;

#50 r = h35;

join

在這個(gè)例子中,各條語句并不是按被執(zhí)行的先后順序給出的,但同樣可以生成前面例子中的波形。

關(guān)鍵詞

在Verilog HDL中,所有的關(guān)鍵詞是事先定義好的確認(rèn)符,用來組織語言結(jié)構(gòu)。關(guān)鍵詞是用小寫字母定義的,因此在編寫原程序時(shí)要注意關(guān)鍵詞的書寫,以避免出錯(cuò)。下面是Verilog HDL中使用的關(guān)鍵詞(請(qǐng)參閱附錄:Verilog語言參考手冊):

always、and、assign、begin、buf、bufif0、bufif1、case、casex、casez、cmos、deassign、default、defparam、disable、edge、else、end、endcase、endmodule、endfunction、endprimitive、endspecify、endtable、endtask、event、for、force、forever、fork、function、highz0、highz1、if、initial、inout、input、integer、join、large、macromodule、medium、module、nand、negedge、nmos、nor、not、notif0、notifl、or、output、parameter、pmos、posedge、primitive、pull0、pull1、pullup、pulldown、rcmos、reg、releses、repeat、mmos、rpmos、rtran、rtranif0、rtranif1、scalared、small、specify、specparam、strength、strong0、strong1、supply0、supply1、table、task、time、tran、tranif0、tranif1、tri、tri0、tri1、triand、trior、trireg、vectored、wait、wand、weak0、weak1、while、wire、wor、xnor、xor。

在編寫Verilog HDL程序時(shí),變量名、端口名、塊名等的定義不要與這些關(guān)鍵詞沖突。

評(píng)論