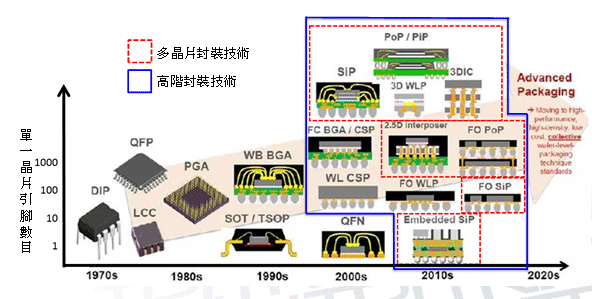

先進封裝工藝WLCSP與SiP的蝴蝶效應

關于先進封裝工藝的話題從未間斷,隨著移動電子產品趨向輕巧、多功能、低功耗發展,高階封裝技術也開始朝著兩大板塊演進,一個是以晶圓級芯片封裝WLCSP(Fan-In WLP、Fan-out WLP等)為首,功能指向在更小的封裝面積下容納更多的引腳數;另一板塊是系統級芯片封裝(SiP),功能指向封裝整合多種功能芯片于一體,壓縮模塊體積,提升芯片系統整體功能性和靈活性。

本文引用地址:http://www.czjhyjcfj.com/article/201610/310984.htm圖1:主要封裝形式演進

Source:拓璞產業研究所整理,2016.9

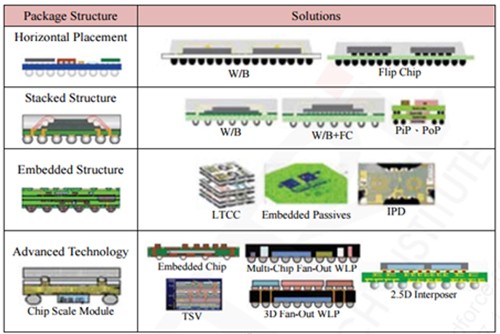

WLCSP:晶圓級芯片封裝(Wafer Level Chip Scale Package)也叫WLP。與傳統封裝工藝相反,WLP是先封裝完后再切割,因此切完后芯片的尺寸幾乎等于原來晶粒的大小,相比傳統封裝工藝,單顆芯片封裝尺寸得到了有效控制。

如何在更小的尺寸芯片上容納更多的引腳數目?WLP技術利用重分布層(RDL)可以直接將芯片與PCB做連接,這樣就省去了傳統封裝DA(Die attach)段的工藝,不僅省去了DA工藝的成本,還降低了整顆封裝顆粒的尺寸與厚度,同時也繞過DA工藝對良率造成的諸多影響。

起初,Fan-In WLP單位面積的引腳數相對于傳統封裝(如FC BGA)有所提升,但植球作業也僅限于芯片尺寸范圍內,當芯片面積縮小的同時,芯片可容納的引腳數反而減少,在這個問題的節點上,Fan-out WLP誕生,實現在芯片范圍外充分利用RDL做連接,以此獲取更多的引腳數。

圖2:從傳統封裝至倒裝封裝及晶圓級封裝結構變化示意圖

Source:拓璞產業研究所整理,2016.9

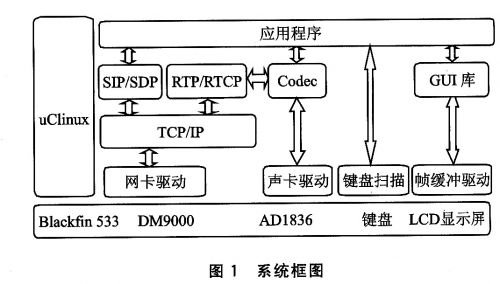

SiP:將不同功能的裸芯片通過整合封裝的方式,形成一個集多種功能于一體的芯片組,有效地突破了SoC(從設計端著手,將不同功能的解決方案集成與一顆裸芯片中)在整合芯片途徑中的限制,極大地降低了設計端和制造端成本,也使得今后芯片整合擁有了客制化的靈活性。

另外由SiP延伸的3D堆疊式封裝技術,通過在垂直方向上增加可放置晶圓的層數來進一步提高SiP的整合能力,可以說作為異質整合的標桿,SiP在超越摩爾定律方面扮演著頭號角色。

圖3:SiP 的基本分類

Source:拓璞產業研究所整理,2016.9

評論