利用新一代虛擬探測功能實現(xiàn)DDR等信號去嵌測試

一、內(nèi)存測試中的難點(diǎn)

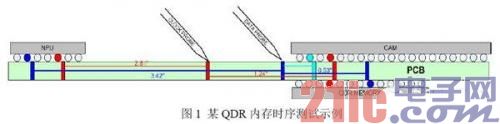

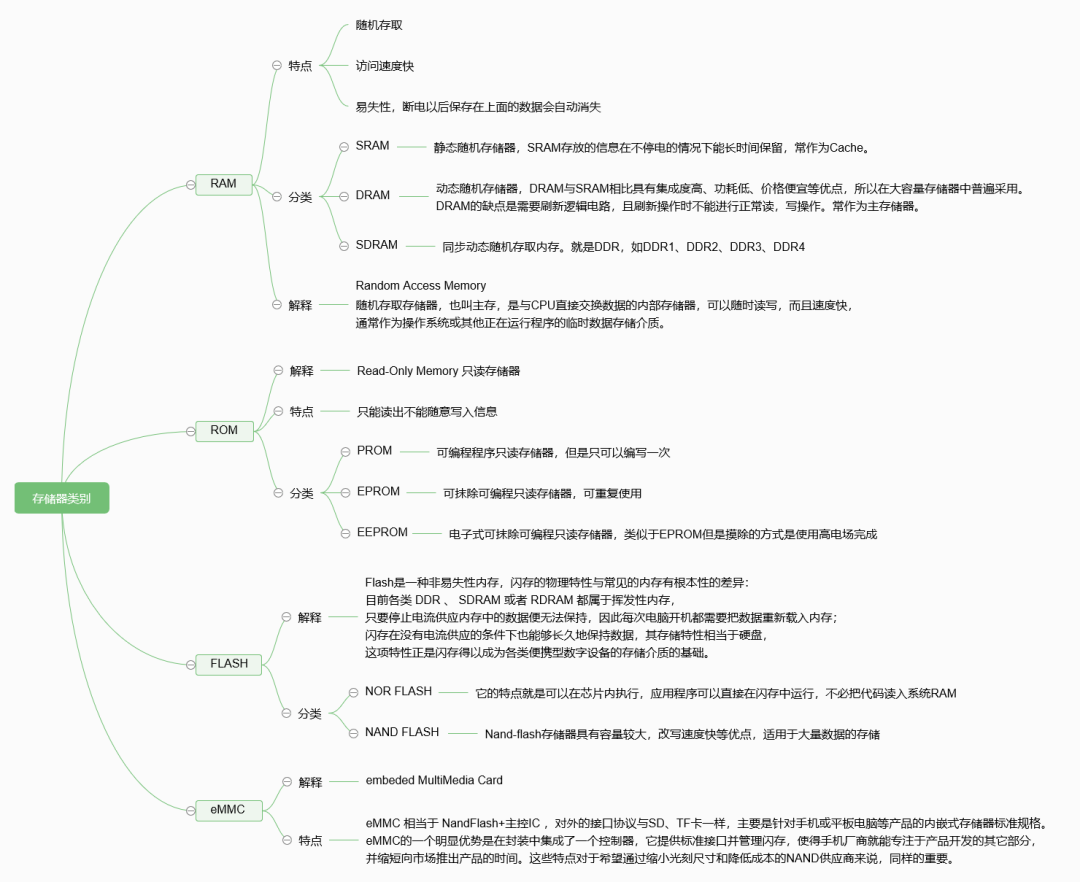

本文引用地址:http://www.czjhyjcfj.com/article/201610/309088.htm內(nèi)存廣泛應(yīng)用于各類電子產(chǎn)品中,內(nèi)存測試也是產(chǎn)品測試中的熱點(diǎn)和難點(diǎn)。內(nèi)存測試中最為關(guān)鍵的測試項目為DQ/DQS/CLK之間的時序關(guān)系。JEDEC規(guī)范規(guī)定測量這幾個信號之間的時序時測試點(diǎn)需要選擇在靠近內(nèi)存的最末端。而當(dāng)前內(nèi)存芯片大部分是BGA封裝,有的甚至是正反貼的,這樣有時候就很難在內(nèi)存芯片的最末端找到測試點(diǎn)進(jìn)行測試,如果在鏈路的中間位置進(jìn)行測試,一方面信號會出現(xiàn)反射回溝等現(xiàn)象,從而影響到時序的測試,另外一方面對不同信號的測試點(diǎn)位置的不同,測量得到的時序就不是真實的時序結(jié)果。如下圖1所示,探頭無法點(diǎn)測到BGA封裝的內(nèi)存芯片的最末端管腳位置,此時準(zhǔn)確的時序測量將會變得非常困難。

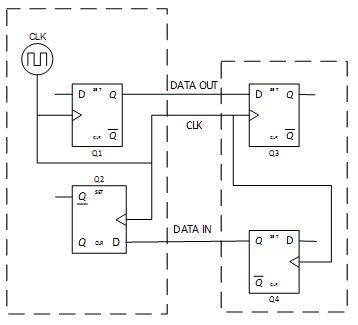

由于在信號鏈路的中間點(diǎn)進(jìn)行的測試,因此信號波形將會因反射而出現(xiàn)明顯的回溝,而且回溝正好出現(xiàn)在時鐘信號上升沿和下降沿的中間位置,這會給時鐘與數(shù)據(jù)之間的時序測量帶來相當(dāng)大的不穩(wěn)定性,測量到的時序和實際情況也將會偏差很大。如下圖2所示,測量到的時鐘波形存在明顯的單調(diào)性問題。

二、通過虛擬探測功能預(yù)測內(nèi)存最末端的波形

力科示波器中的虛擬探測有如下兩種方法:

1、使用EyeDoctorII軟件的通道仿真功能

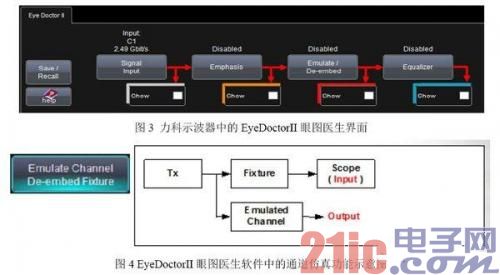

使用該方法需要設(shè)法獲得測試點(diǎn)到鏈路末端的S參數(shù),然后將S參數(shù)帶入到示波器的EyeDoctorII眼圖醫(yī)生軟件中(如圖3所示界面)即可預(yù)測到末端信號的波形。但在實際應(yīng)用中,由于測試點(diǎn)可能只是個過孔,測試點(diǎn)位于鏈路的中間,且也無法從測試點(diǎn)位置將鏈路斷開成兩部分,這樣就很難測量得到測試點(diǎn)位置至鏈路最末端的S參數(shù)。如果通過軟件從PCB板上進(jìn)行S參數(shù)的提取會更加容易些,但是仿真的結(jié)果和實際情況還是會存在一定的差別。

2、使用力科示波器中的VP@Receiver虛擬探測功能

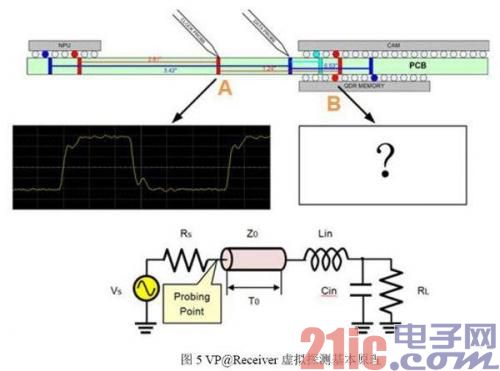

VP@Receiver的基本原理是先獲得測試點(diǎn)到鏈路末端的傳輸線的延時Td、傳輸線末端的匹配模型(電容C,電感L,阻抗Z),然后將這些參數(shù)應(yīng)用到實測到的波形上并推測出鏈路最末端的信號波形。下面以一個實例為例說明如何使用VP@Receiver來實現(xiàn)虛擬探測功能:

如下圖5所示,我們能夠通過示波器測量得到A點(diǎn)的信號波形,然后我們需要利用這個波形通過虛擬探測得到B點(diǎn)的波形。

為了獲得這個波形,我們將測試點(diǎn)A點(diǎn)和鏈路末端B點(diǎn)之間的傳輸鏈路等效為上圖5下方的電路模型。電路模型的主要參數(shù)包括鏈路傳輸延時T0,輸入端電感Lin,輸入端電容Cin,輸入端阻抗RL. 為了獲得這些參數(shù),我們先通過力科示波器中的Jitter Sim功能獲得一個和被測波形(即可以測量得到的A點(diǎn)波形的信號特征)各項參數(shù)(如幅度,周期,上升時間等)非常接近的理想的波形。Jitter Sim是力科示波器中的一個通過軟件仿真的方法實現(xiàn)信號源的功能,該功能可以實現(xiàn)時鐘信號,正弦信號,NRZ,RZ等種類多樣的碼型。而且可以施加抖動,過沖,設(shè)置幅度,頻率,偏置,截至頻率,上升時間,下腳時間等等。如下圖6所示。

根據(jù)A點(diǎn)信號的波形和反射位置我們可以測量出信號的頻率約為156MHz,反射時間約為257ps.下圖7中M1為實測波形,Z1為實測波形的局部放大,F(xiàn)1為通過Jitter Sim仿真得到的波形,Z2為對仿真波形的局部放大。仿真波形與實測波形具有非常接近的幅度,頻率,上升時間,占空比等特性。

上圖7中通過Jitter Sim仿真得到的波形F1是沒有施加匹配模型的,下面我們通過VP@Receiver來為F1波形施加匹配,使用F2函數(shù)實現(xiàn)VP@Receiver功能。如下圖8所示,分別輸入傳輸演示Td(130ps),阻抗Z(50ohms),寄生電容(2.8pf),寄生電容我們可以以芯片的輸入電容為參考,然后根據(jù)仿真波形與實測波形的吻合程度進(jìn)行調(diào)節(jié)。

施加了上述匹配后,仿真波形如下圖9所示,我們看到施加傳輸線模型和匹配后,仿真得到的Z2的波形和實測波形Z1非常的接近(尤其是因反射導(dǎo)致的回溝的位置)。這說明匹配模型和傳輸線模型與實際情況是非常吻合的。這樣我們就可以將該傳輸線模型和匹配模型應(yīng)用到我們實際測量得到的波形上,虛擬探測出末端位置的真實波形。我們只要將上圖8中的VP@Receiver的工作模式從“Sim”切換到“Term”,F(xiàn)2函數(shù)(VP@Receiver)的輸入源由F1修改為實測波形M1,即可得到鏈路末端的波形,虛擬探測到的波形如圖10所示,由于虛擬探測到的波形在鏈路末端,所以因反射引起的回溝已經(jīng)消失了。

圖11為本文開頭提到的某QDR的時鐘與數(shù)據(jù)之間的時序測量示例。由于時鐘信號的回溝導(dǎo)致無法穩(wěn)定的測量時序,因此必須要通過虛擬探測的方法探測到鏈路最末端的時鐘和數(shù)據(jù)波形,才能夠正確的進(jìn)行時序的測量。

三、小結(jié)

本文通過實例應(yīng)用介紹了Teledyne LeCroy(力科)示波器中的一個獨(dú)特的虛擬探測VP@Receiver功能。通過該虛擬探測功能可以解決實際測量中無法直接探測到鏈路末端波形的困難。而隨著單板密度的日益增加以及BGA封裝的普遍使用,在鏈路末端進(jìn)行波形的探測變得越來越困難,尤其是DDR內(nèi)存的時序測量中該問題尤其變得更加明顯。力科的VP@Receiver虛擬探測功能將為解決這一困難提供一個方法和思路。

評論