單片機與A/D轉換器的接口設計

MAX195是16位逐次逼近方式的ADC。它將高精度、高速度、低電源功耗(消耗電流僅10μA)的關閉方式等性能結合在一起。內部校準電路對線性度與偏置誤差進行校正,所以無需外部調整便可達到全部額定的性能指標。電容性的DAC結構使之具有特有的85kbps跟蹤/保持功能,變換時間僅需9.4μs。三態串行數據輸出及引腳可選的單極性(0~VREF)或雙極性(-VREF~+VREF)的輸入范圍使之可廣泛應用于便攜式儀表、醫用信號采集及多傳感器測量等系統中。

本文引用地址:http://www.czjhyjcfj.com/article/201610/307671.htm1 MAX195引腳及說明

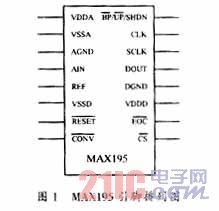

MAX195有16個引腳,其排列如圖1所示。

2 MAX195轉換原理及時序

MAX195片內含有電容性的數字模擬變換器(DAC),可對模擬輸入進行特有的跟蹤和保持,再由逐次逼近寄存器和比較器,在變換時鐘CLK的控制下,把模擬輸入變換成16位數字代碼,通過片內的串行接口輸出。芯片內的接口和控制邏輯易與大多數微處理器相連,減少了對外部元件的需求。

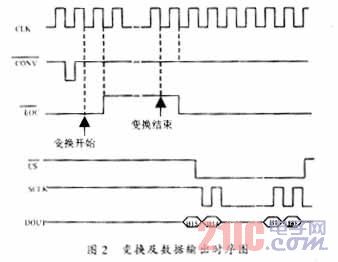

其變換及數據輸出的時序如圖2所示。

由時序可以看出,在前次變換結束至少經過三個或三個以上時鐘周期后,變換在有效后的CLK時鐘下降沿開始(MAX195對信號的跟蹤/保持、采集需4個CLK周期)。同時,在下一個時鐘下降沿變高,待經過9.4μs(CLK為1.7MHz)變換結束后,由高變低,給出變換結束信號,可送去中斷或被查詢。變換結束由三態串行口DOUT端輸出。在變換期間由CLK控制讀出數據,也可在兩次變換之間由SCLK串行時鐘定時讀出數據,最高速率可達5Mbps。圖2中所示情況為后者,在保持低電平后,在每個SCLK的下降沿,DOUT端按MSB在前的次序輸出一位數據,否則,DOUT處于高阻態。

3 MAX195的校準

MAX195在上電時自動進行校準。為了減少噪聲的影響,每一個校準試驗進行多次并對其結果求平均值。在時鐘頻率1.7MHz下,校準大約需14000個時鐘周期或8.2ms。除了上電校準之外,把拉至低電平將使MAX195暫停工作,使再次回到高電平便啟動一次新的校準。

注:只有在上電延遲期間,電源尚未穩定就開始上電校準或電源電壓、環境溫度及時鐘頻率發生明顯變化時,才建議重新加以校準。

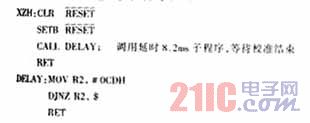

軟件校準參考子程序如下:

4 AT89C51與MAX195的接口設計

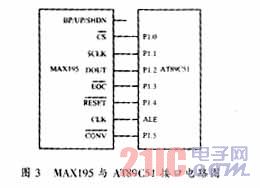

圖3為AT89C51與MAX195接口的硬件電路圖。

圖中AT89C51的ALE端輸出信號(等于1/6晶振頻率fosc=6MHz)作為CLK變換時鐘。P1.5作為MAX195的啟動控制端。端懸空表示模擬信號可雙極性輸入,也可根據需要接+5V———單極性輸入;接地———關閉方式。

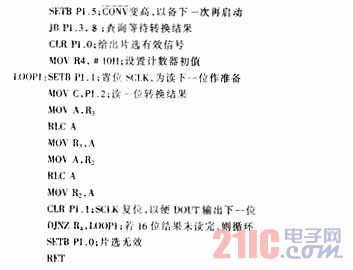

根據圖3,給出A/D采樣程序如下:

注:采樣結果保存在R2、R33中。

評論