基于PLD的納秒級脈沖發生器

1 基本原理

本文引用地址:http://www.czjhyjcfj.com/article/192124.htm設計采用的XILINX公司的復雜可編程邏輯器件(CPLD)幾乎可適用于所有的門陣列和各種規模的數字集成電路,他以其編程方便、集成度高、速度快、價格低等特點越來越受到設計者的歡迎。選用的CPLD為XILINX公司的XC9572XL,屬于XC9500系列,是目前業界速度較快的高集成度可編程邏輯器件。

CPLD開發軟件用ISE 6.0+ModelSim 5.7SE,該軟件是一個完全集成化、易學易用的可編程邏輯設計環境,并且廣泛支持各種硬件描述語言。他還具有與結構無關性、多平臺運行、豐富的設計庫和模塊化的工具等許多功能特點。

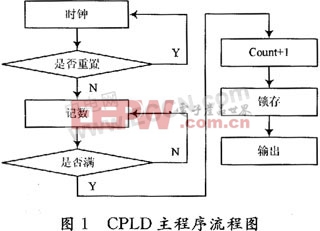

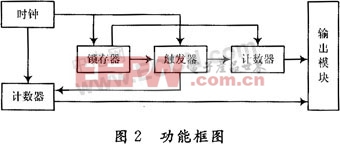

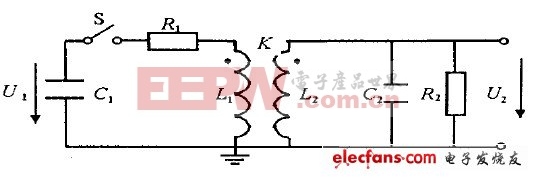

CPLD主程序流程圖如圖1所示,時針信號是整個程序的關鍵,通過時鐘對各個模塊進行精確控制,實現基本功能。時鐘信號的精準度決定了輸出脈沖信號的精準度。時鐘源采用了4腳晶振,可以輸出一個穩定的時鐘信號。CPLD內部電路資源分配如圖2所示。

|

時鐘信號和復位信號作為輸入信號,控制脈沖信號的輸出。系統分4個模塊,包括計數器、鎖存器、觸發器和數據輸出模塊。時鐘信號和復位信號分別加在計數器和觸發器上,計數器計數通過鎖存,在時鐘信號作用下同步觸發輸出信號。當復位信號到來時,計數器重新清零計數。

|

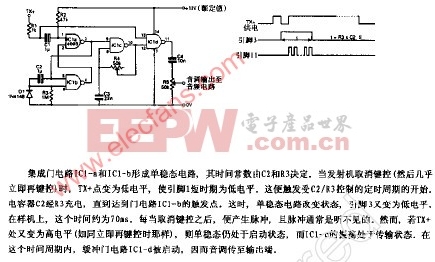

當時鐘的上升沿到來時對高頻時鐘進行計數,CPLD內部建立一個5位計數器,計數器滿后自動重置為0,輸出端把計數器的各位進行輸出,計數器滿后也輸出一個高電平。第一級輸出端一共有7個,可以實現對時鐘的2,4,8,16,32,64分頻以及單脈沖輸出。在CPLD內部再建立一個3位計數器,對前級4分頻信號再做計數,調節占空比,控制脈沖輸出,同時對一級分頻信號進行相與輸出。設置一個復位端,當高電平時候,對電路進行復位,計數器重新開始工作。通過復位端可以很好地控制脈沖輸出,并且輸出信號脈沖寬度在不同的分頻接口可以得到不同的脈沖寬度信號,也可以通過修改程序實現脈沖寬度的改變。CPLD外圍硬件電路包括了電源、晶振、輸出端口、指示燈,如圖3所示。

相關推薦

技術專區 |

評論