貫穿整個IC實現流程的集成化低功耗設計技術

降低功耗是現代芯片設計最具挑戰性需求之一。采用單點工具流程時,往往只有到了設計流程后期階段才會去考慮降低功耗的需求,從而經常導致大量問題和延時。微捷碼設計自動化有限公司高級技術產品經理Rob Knoth向我們解釋了‘為何功率優化應是完整設計流程必不可少的集成組件’。

本文引用地址:http://www.czjhyjcfj.com/article/180912.htm起初,低功耗設計技術主要是用于移動產品。而今插在電源插座上的產品數不勝數,它們都在不斷吸收著電流,全世界大量功率都浪費在了這些產品上。今天,政府正積極要求電子企業遵從更嚴格的要求來幫助降低全球功耗。低功耗設計與每個人息息相關。現在低功耗需求無處不在,而且變得更具挑戰性。

低功耗設計,不論是動態功耗還是靜態功耗,均要求設計流程各個階段時序、功耗和面積間復雜的折衷權衡。這些需求相互間聯系密切,要想解決這些需求,低功耗分析和優化引擎必須集成并運用于從RTL規格到GDSII輸出的整個流程中。由于芯片尺寸還在持續增長,因此這一流程必須是可縮放的,否則它將會對設計師工作效率造成限制。

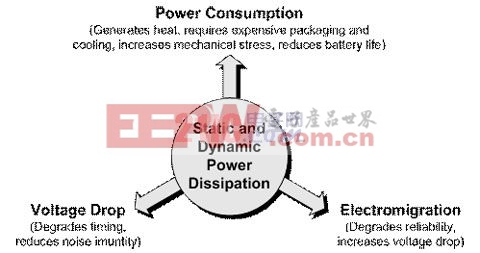

圖1: 低功耗設計牽涉到設計流程的各個方面

動態功耗

設計的動態功耗是由電容、電壓和頻率共同決定的。

電容主要受到門極電路尺寸及布線的影響。邏輯門尺寸是降低內部開關電流與增加系統面積、噪音和容性負載間的一種折衷權衡。縮短布線將意味著容性負載的減少,但是帶來擁塞情況的惡化,可能導致布線違規或源自串擾的時序問題。

頻率對系統動態功耗的影響很大。采用并行處理方式,系統時鐘可以降低,同時保持吞吐量不變。當然這是以犧牲面積為代價,是從架構上進行考慮。

在芯片總功耗中,時鐘樹網絡的功耗占據了很大一部分。將功耗作為一個成本函數來考慮已變得越來越重要,特別在較小尺寸中更是如此。目前已有各種不同技術可被廣泛應用于RTL綜合和物理綜合中,如:廣泛的門控時鐘覆蓋、門控時鐘克隆/反克隆、有功率意識的緩沖器插入、尺寸調整和門控時鐘布局。此外,如時鐘樹綜合(CTS)中多閾值電壓(Multi-Vt)、層次化時鐘門控、基于行為的時鐘門控等其他技術也可以提供額外的功率節省。門控技術降低動態功耗也必須在面積和靜態功耗上平衡折中。

評論