電源設計小貼士 41:DDR 內存電源

CMOS 邏輯系統的功耗主要與時鐘頻率、系統內各柵極的輸入電容以及電源電壓有關。器件形體尺寸減小后,電源電壓也隨之降低,從而在柵極層大大降低功耗。這種低電壓器件擁有更低的功耗和更高的運行速度,允許系統時鐘頻率升高至千兆赫茲級別。在這些高時鐘頻率下,阻抗控制、正確的總線終止和最小交叉耦合,帶來高保真度的時鐘信號。傳統上,邏輯系統僅對一個時鐘沿的數據計時,而雙倍數據速率 (DDR) 內存同時對時鐘的前沿和下降沿計時。它使數據通過速度翻了一倍,且系統功耗增加極少。

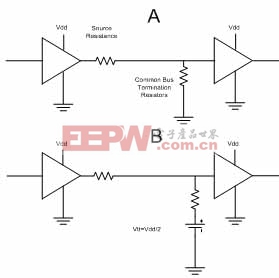

本文引用地址:http://www.czjhyjcfj.com/article/178232.htm高數據速率要求時鐘分配網絡設計要倍加小心,以此來最小化振鈴和反射效應,否則可能會導致對邏輯器件非有意計時。圖 1 顯示了兩種備選總線終止方案。第一種方案(A)中,總線終止電阻器放置于分配網絡的末端,并連接至接地。如果總線驅動器處于低態下,電阻器的功耗便為零。在高態下時,電阻器功耗等于電源電壓(VDD)平方除以總線電阻(源阻抗加端接電阻)。平均功耗為電源電壓平方除以兩倍總線電阻。

圖 1 VTT 端接電壓降低一半端接功耗

評論