68HC908JB8單片機及其在USB外設系統中的應用

主要參數及引腳功能

本文引用地址:http://www.czjhyjcfj.com/article/171966.htmMC68HC908JB8是采用HCMOS工藝技術生產的高性能單片機芯片,具有片內256BRAM和8KB的Flash ROM結構,16位雙通道TIM模塊(每一通道配有輸入捕捉、輸出比較和PWM工作模式),以及兼容USB1.1協議低速通信功能。

JB8 的性能

68HC908JB8是一種高性能M68HC08結構,它和M6805、M146805及M68HC05族代碼兼容,3MHz內部總線頻率,256B的 RAM和8129字節的Flash存儲器,且在片內可編程。最多可達37個一般3.3V的I/O口。其中包括:

因封裝不同有13或10個共享I/O腳

·因封裝不同有24、22、8、或2個專用I/O腳

·端口A有8個鍵盤中斷

·6個10mA的驅動LED腳

·2個25mA紅外LED腳

·2個在USB模塊禁止情況下,對于PS/2連接有10mA的高電流驅動腳

16位雙通道TIM兼容USB1.1協議的低速器件,其中數據傳輸速率為1.5Mbps,內置3.3V的電壓調節器。Endpoint0 有8字節的發射緩沖器和8字節的接收緩沖器;Endpoint1 有8字節的發射緩沖器;Endpoint2有8字節的發射緩沖器及8字節接收緩沖器。

系統保護特征包括可選COP復位、可選LVI復位、非法代碼復位及非法地址復位。

低功耗設計有完全靜態STOP模式和WAIT模式,內部連接上拉電阻的主復位腳,以及上電復位和外部異步中斷( IRQ)。

引腳功能

JB8單片機有44腳(QFP封裝)、42腳(SDIP封裝)、28腳(PDIP/SOIC封裝)及20腳(PDIP/SOIC封裝),現以44引腳芯片(如圖1)為例,說明各腳的功能。

VDD和VSS分別為電源和地引腳,VREG為3.3V輸出,其主要用于USB數據驅動的電壓調制,OSC1、OSC2為時鐘引腳,RST外部復位引腳, RST是雙向的,該引腳包含一個對VDD的上拉電阻;IRQ:外部異步中斷引腳,它也可編程進入監控模式,該引腳包含一個對VDD的上拉電阻; PTE4/D-也可編程對IRQ1中斷進行觸發,也可編程為USB D-引腳;PTA7/KBA7~PTA0/KBA0:雙向I/O引腳,可編程作為外部鍵盤中斷引腳;PTB7~PTB0:雙向I/O引腳; PTC7~PTC0:雙向I/O引腳;PTD7~PTD0:雙向I/O引腳;引腳E是5位具有特殊功能的引腳,其中PTE4/D-、PTE3/D+同 USB數據總線D-、D+共享,其他3個引腳同定時器模快連接。當USB模塊禁止時,PTE4,PTE3成為驅動電流10mA的引腳,且包含5KΩ的上拉電阻;當USB 模快使能時,PTE4/D-和PTE3/D+成為USB的D-和D+。PTE2/TCH1、PTE1/TCH0、PTE0/TCLK為共享引腳。

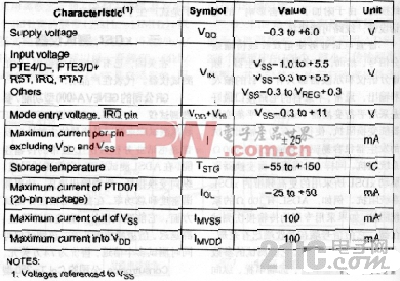

表1 68HC908JB8性能指標

MC68HC908JB8內部包含保護電路,但在使用時應盡量使電壓低于表1中所給的最大值,即VSS ≤VIN或 VOUT≤ VREG。當芯片工作時,不用的引腳要連接到適當的VSS 或VREG上。

評論