- 賈凡尼現(xiàn)象或賈凡尼效應(yīng)是指兩種金屬由于存在電位差,通過介質(zhì)產(chǎn)生了電流,繼而產(chǎn)生了電化學(xué)反應(yīng),致使電位高的陽極被氧化的現(xiàn)象.本文中我們將各方面探討分析PCB化學(xué)鍍銀工藝中賈凡尼現(xiàn)象存在的原因和處理方法。

- 關(guān)鍵字:

PCB 化學(xué)鍍銀 工藝 分析

- 敷銅作為PCB設(shè)計的一個重要環(huán)節(jié),不管是國產(chǎn)的青越鋒PCB設(shè)計軟件,還國外的一些Protel,PowerPCB都提供了智能敷銅功能,那么怎樣才能敷好銅,我將自己一些想法與大家一起分享,希望能給同行帶來益處。 所謂覆銅

- 關(guān)鍵字:

PCB 敷銅 工藝

- 一. 引言

隨著人類對于居住環(huán)境要求的不斷提高,目前PCB生產(chǎn)過程中涉及到的環(huán)境問題顯得尤為突出。目前有關(guān)鉛和溴的話題是最熱門的;無鉛化和無鹵化將在很多方面影響著PCB的發(fā)展。雖然目前來看,PCB的表面處理工

- 關(guān)鍵字:

PCB 表面處理 工藝

- 本文以比較器為基本電路,采用恒流源充放電技術(shù),設(shè)計了一種基于1.0mu;m CMOS工藝的鋸齒波振蕩電路,并對其各單元組成電路的設(shè)計進(jìn)行了闡述。同時利用Cadence Hspice仿真工具對電路進(jìn)行了仿真模擬,結(jié)果表明,鋸

- 關(guān)鍵字:

CMOS 工藝 鋸齒波 振蕩電路

- 1 引言 本文在傳統(tǒng)鎖相環(huán)結(jié)構(gòu)的基礎(chǔ)上進(jìn)行改進(jìn),設(shè)計了一款用于多路輸出時鐘緩沖器中的鎖相環(huán),其主 要結(jié)構(gòu)包括分頻器、鑒頻鑒相器(PFD)、電荷泵、環(huán)路濾波器和壓控振蕩器(VCO)。在鑒相器前采用預(yù) 分頻結(jié)構(gòu)減小

- 關(guān)鍵字:

CSMC PLL 工藝 零延時

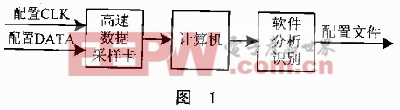

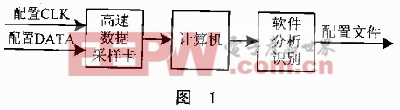

- 在現(xiàn)代電子系統(tǒng)設(shè)計中,由于可編程邏輯器件的卓越性能、靈活方便的可升級特性,而得到了廣泛的應(yīng)用。由于大規(guī)模高密度可編程邏輯器件多采用SRAM工藝,要求每次上電,對FPGA器件進(jìn)行重配置,這就使得可以通過監(jiān)視配置

- 關(guān)鍵字:

保密性 問題 FPGA 工藝 SRAM 基于

- 利用PLC系統(tǒng)控制閃光對焊工藝過程的設(shè)計,閃光對焊作為一種先進(jìn)的焊接技術(shù),具有無需添加焊接材料、生產(chǎn)率高、成本低、易于操作等優(yōu)點(diǎn)。隨著工業(yè)技術(shù)的不斷發(fā)展,焊接的零件截面越來越大,遇到了一些技術(shù)問題,如焊接加熱難、生產(chǎn)率低、產(chǎn)品合格率低等。為了

- 關(guān)鍵字:

工藝 過程 設(shè)計 閃光 控制 PLC 系統(tǒng) 利用

- 工業(yè)以太網(wǎng)是一個基于以太網(wǎng)技術(shù)標(biāo)準(zhǔn)進(jìn)行實(shí)現(xiàn)所有控制、調(diào)節(jié)儀器設(shè)備自動化技術(shù)的高層次概念。因為一般情況下企業(yè)已擁有把辦公計算機(jī)連接成為一個網(wǎng)絡(luò)的LAN以太網(wǎng)了,而這種網(wǎng)絡(luò)有可能與工業(yè)以太網(wǎng)聯(lián)網(wǎng),并且仍然使用

- 關(guān)鍵字:

設(shè)計 方案 聯(lián)網(wǎng) 垂直 工藝 設(shè)備 流程

- 實(shí)現(xiàn)世界上最先進(jìn)的定制邏輯器件引言

Altera于2008年第二季度推出Stratix® IV和HardCopy® IV器件系列標(biāo)志著世界上首款40-nm FPGA和業(yè)界唯一

40-nm ASIC 無風(fēng)險移植途徑的誕生。Altera 通過三年周密的規(guī)劃和

- 關(guān)鍵字:

40 nm 工藝 定制

- SMT小型電子產(chǎn)品的安裝是高等職業(yè)學(xué)校應(yīng)用電子技術(shù)專業(yè)中《電子產(chǎn)品工藝實(shí)訓(xùn)》課程的一個重要項目。結(jié)合《電子產(chǎn)品工藝》這門課程的特點(diǎn),我們在電子實(shí)訓(xùn)環(huán)節(jié)采用了項目教學(xué)模式,即師生雙方共同在實(shí)訓(xùn)室參與項目教學(xué)

- 關(guān)鍵字:

環(huán)節(jié) 應(yīng)用 工藝 電子 教學(xué) 項目

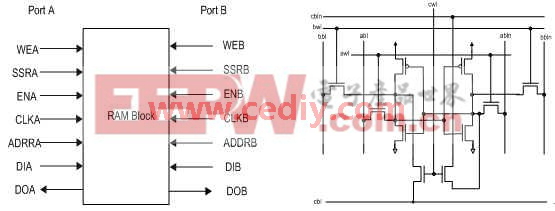

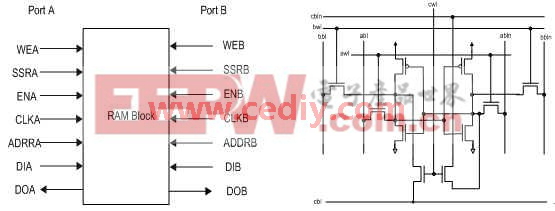

- 基于0.13微米CMOS工藝下平臺式FPGA中可重構(gòu)RAM模塊的一種設(shè)計方法,1. 引言

對于需要大的片上存儲器的各種不同的應(yīng)用,F(xiàn)PGA 需要提供可重構(gòu)且可串聯(lián)的存儲器陣列。通過不同的配置選擇,嵌入式存儲器陣列可以被合并從而達(dá)到位寬或字深的擴(kuò)展并且可以作為單端口,雙端口

- 關(guān)鍵字:

RAM 重構(gòu) 模塊 設(shè)計 方法 FPGA 平臺 0.13 微米 CMOS 工藝

- 0 引言

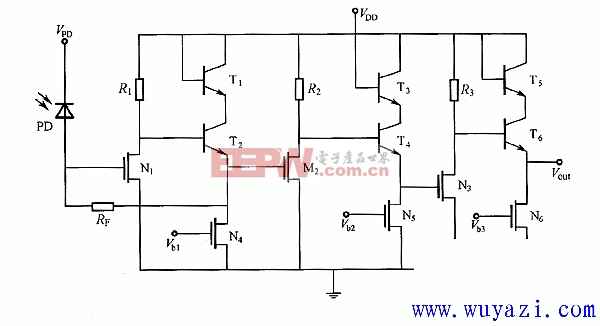

運(yùn)算放大器是數(shù)據(jù)采樣電路中的關(guān)鍵部分,如流水線模數(shù)轉(zhuǎn)換器等。在此類設(shè)計中,速度和精度是兩個重要因素,而這兩方面的因素都是由運(yùn)放的各種性能來決定的。

本文設(shè)計的帶共模反饋的兩級高增益運(yùn)

- 關(guān)鍵字:

CMOS 工藝 放大器 全差分

- 針對DC-DC電源管理系統(tǒng)中所必須的欠壓鎖存(UVLO)功能,提出一種改進(jìn)的欠壓鎖存電路。所設(shè)計的電路在不使用額外的帶隙基準(zhǔn)電壓源作為比較基準(zhǔn)的情況下,實(shí)現(xiàn)了閾值點(diǎn)電位、比較器的滯回區(qū)間等參量的穩(wěn)定。整個電路采用CSMC0.5 μm BCD工藝設(shè)計,使用HSpice軟件仿真,結(jié)果表明所設(shè)計的UVLO電路具有結(jié)構(gòu)簡單、反應(yīng)靈敏、溫度漂移小、功耗低等特點(diǎn)。

- 關(guān)鍵字:

電路設(shè)計 工藝 BCD 基于

- 半導(dǎo)體設(shè)備和材料企業(yè)的技術(shù)提升及創(chuàng)新要從研究材料入手,從源頭上達(dá)到國際先進(jìn)水平。在工業(yè)制備方面要加強(qiáng)新型工藝的開發(fā)和應(yīng)用。我國半導(dǎo)體設(shè)備性能、控制已達(dá)到國際高端水平,但穩(wěn)定性還待提升。另外,需要做高端設(shè)備工藝方面的提升和研究。

蘭州瑞德自主開發(fā)的產(chǎn)品涉及多行業(yè)、多領(lǐng)域,在國際金融危機(jī)期間,遇到的問題主要在工藝應(yīng)用和需求行業(yè)比例發(fā)生變化方面,公司根據(jù)各行業(yè)特點(diǎn),公司采取新品上市、設(shè)備改制、設(shè)備派生等手段,使研、切、拋電子專用設(shè)備進(jìn)入各行業(yè)的速度加快了,尤其是視窗、光學(xué)等行業(yè)。半導(dǎo)體行業(yè)仍主打高端設(shè)

- 關(guān)鍵字:

半導(dǎo)體設(shè)備 工藝

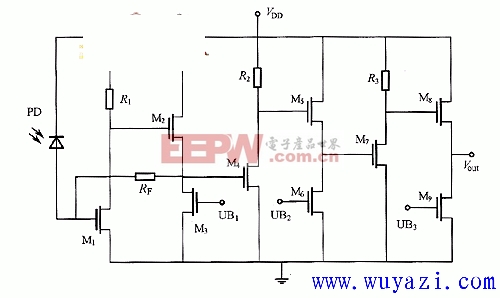

- 近年來,軟件無線電(Software Radio)的技術(shù)受到廣泛的關(guān)注。理想的軟件無線電臺要求對天線接收的模擬信號經(jīng)過放大后直接采樣,但是由于通常射頻頻率(GHz頻段)過高,技術(shù)上所限難以實(shí)現(xiàn),而多采用中頻采樣的方法。而對

- 關(guān)鍵字:

Telescopic 0.13 CMOS 工藝

工藝介紹

您好,目前還沒有人創(chuàng)建詞條工藝!

歡迎您創(chuàng)建該詞條,闡述對工藝的理解,并與今后在此搜索工藝的朋友們分享。

創(chuàng)建詞條

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473