SERDES的FPGA實現(07-100)

時鐘數據恢復

本文引用地址:http://www.czjhyjcfj.com/article/91924.htm時鐘數據恢復(CDR)接收機必須恢復來自數據的嵌入式時鐘。更確切地說,時鐘起源于數據信令的開關轉換。CDR發送到串行化數據開始,然后,變換數據為8b/10b(或類似的編碼方法)。編碼取8位數據,并變換此數據為10位符號。8b/10b編碼在數據線上提供一個相等“0”和“1”傳輸。這會減弱符號間干擾,并提供足夠的數據沿,使接收機鎖相在輸入數據流。發送器將增加系統時鐘到發送位率,并以此位率發送8b/10b數據到TX差分對。

CDR接收器的工作從在RX差分位流上鎖相開始。然后,接收器在每個恢復時鐘位校準數據。下一步,數據在接收器的參考時鐘校準字。最后,數據是8b/10b譯碼,準備用于系統。在CDR系統中,發送和接收系統,通常具有獨立的系統時鐘。兩個時鐘都處在特定的變化要求內,這是關鍵。此閾值是幾百PPM(百萬分率)量級。

CDR接口的主要設計問題是抖動。抖動是實際數據傳輸布局的相對理想狀況。總抖動(TJ)是由確定性抖動和隨機抖動組成。大部分抖動是確定性的,其分量包括符號間干擾、占空比失真和同期抖動(即來自開關電源的干擾)。隨機抖動往往是半導體熱問題的副產物,而難斷定。發送參考時鐘、發送PLL、串行器和高速輸出緩沖器,都對發送抖動有貢獻。發送抖動通常標定為給定位周期或數據眼圖的單位間隔(UI)百分比。例如,抖動.2UI表示抖動為位周期20%。對于發送抖動,U1數越小越好,這表明抖動較小。

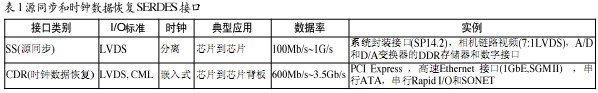

表1 源同步和時鐘數據恢復

同樣,CDR接收器標定在給定的位率所允許的最大抖動值。典型的誤碼率標準是1e-12(每1e 12位一個誤差)。接收抖動也標定為U1。U1越大,表明接收機可以允許更大抖動。典型接收機指標是.8U1,這意味著位周期的80%可以是噪聲,而接收機仍然能夠可靠地接收數據。抖動通常用統計bell分布量化表示。

SERDES測試和眼圖

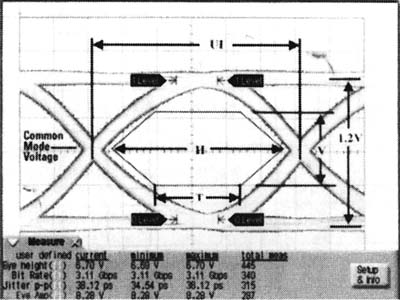

由于抖動是SERDES系統中的主要解決的問題,所以,抖動也是測試測量的一個焦點。測量抖動是用高性能示波器連接SERDES信號,觀測“數據眼圖”。對于給定差分對r的眼圖是很多狀態過渡的重疊。取樣窗口足夠的寬,能保證包含圖中的兩個交叉點。這種合成圖看起來象一個眼睛,此圖提供信號質量和抖動的直觀目測方法。總之,眼睛打開越寬,信號越好。

圖2示出在示波器上看到的典型眼圖。在此眼圖中,V量測對1.2V總電壓擺幅(從邏輯O到邏輯1)的眼打開的高度。有3個寬度(或時間)測量:U1量測全位周期,H量測共模電壓下全打開,T量測最小和最大解扣電壓間的寬度。H、T和V值越大,表明眼睛越寬、因而,信號越好,抖動越小。

圖2 數據眼圖

評論