DDR2 SDRAM介紹及其基于MPC8548 CPU的硬件設計(08-100)

DDR2 SDRAM接口的信號線分為4組,以下以MPC8548命名方式為準,命名和DDR2 SDRAM芯片資料的區別在于信號名之前多一個字母”M”【7】:

本文引用地址:http://www.czjhyjcfj.com/article/91686.htm1) 數據組:MDQS/MDQS#[8:0], MDM[8:0], MDQ[63:0], MECC[7:0]

2) 地址組:MBA[2:0], MA[15:0], MRAS#, MCAS#, MWE#

3) 命令組:MCS#[3:0], MCKE[3:0], MODT[3:0]

4) 時鐘組:MCK/MCK#[5:0]

PCB設計時,建議布線順序依次為:數據組,地址組,控制組,時鐘組,電源。

對于單端信號線,阻抗控制在50~60歐姆內。對于差分信號線,阻抗控制在100~120歐姆內。

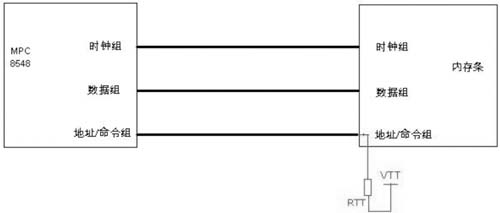

如果使能了ODT功能,數據組無需外部匹配電阻,走線直接從MPC8548連接到內存條即可。而地址組和命令組需要在內存條末端利用外部電阻RTT上拉到VTT電平實現匹配,電阻值需要經過仿真確定。如圖6,考慮到最佳的信號完整性,RTT應該放在內存條之后,即地址/命令組信號走線從MPC8548出來,應該先到內存條的引腳,然后再走到RTT電源平面實現終端匹配。對于時鐘組,一般而言,內存條上都包含了100~120歐姆的差分終端電阻,所以在PCB上無需外加匹配。

圖6 MPC8548和DDR2 SDRAM內存條硬件接口設計

由于本設計采用8位的DDR2 SDRAM芯片,因此,對數據組可以分為9個小組:MDQS/MDQS#[0],MDQ[7:0],MDM0為第一組;MDQS/MDQS#[1], MDQ[15:8],MDM1為第二組;依次類推;MDQS/MDQS#[8],MECC[7:0],MDM8為第九組。對這九小組數據線,要求各小組之內,走線在同一層并擁有相同數目的過孔,走線長度差異控制在20mil之內,所有的信號線走線必須以完整的地層作為參考。不同小組之間,走線長度差異控制在500mil之內。對每一小組,小組內的8根MDQS信號線的線序可以根據走線方便的目的進行調整。需要注意,在本設計中,采用的內存條上的存儲芯片是8位的(即內存條上每片DDR SDRAM芯片有8根DQ數據線),因此每8位MDQ信號歸為一個小組,市場上還有許多4位,16位的內存條,如果需要兼容這些內存條,硬件設計中需要注意應該以每4位MDQ信號歸為一個小組。數據組的信號線和其他組的信號線間距要求在25mil以上,數據組內信號線間距要求在10mil以上。對于差分的MDQS和MDQS#信號,走線長度差異應該控制在10mil之內。

對地址/命令組,該組內信號線長度差異應控制在100mil之內。走線以1.8V電源平面或完整的地層作為參考層。走線和其他組的信號線間距保證在25mil以上。該組內信號線間距保證在10mil以上。

對時鐘組,差分信號對內走線長度差異控制在10mil內,盡量在同一層內走線,如果需要換層,兩根差分信號應該一起換層。與其他組的信號間距在25mil以上。在MPC8548一側,一共提供了6對相位相同的時鐘對,即MCK/MCK#[5:0],其目的是為了兼容內存條設計和分立的內存芯片設計。例如在本設計中,如果選用分立的8位存儲芯片,一共需要9片,如果MPC8548只提供一對時鐘對,其驅動能力顯然無以滿足9片存儲芯片,因此需要由MPC8548提供更多的時鐘對輸出。如果選用內存條,需要根據內存條的不同種類來決定需要使用多少對時鐘對。根據對MCK/MCK#信號是否提供驅動,內存條可以分為Buffered DIMM(緩沖驅動式內存條)和Unbuffered DIMM (非緩沖驅動式內存條),對于前者而言,由于MCK/MCK#在內存條上需要經過緩沖再送到DDR2 SDRAM芯片,即在內存條上利用緩沖器(通常是帶鎖相環的緩沖器)保證了該信號的驅動能力,所以只需要MPC8548提供一對時鐘對(例如MCK/ MCK#[0])送到內存條即可。對于后者而言,內存條上不提供對時鐘對的驅動,通過計算可以知道從MPC8548提供的每對時鐘對,能可靠驅動3個DDR2 SDRAM芯片作為負載。因此需要使用MPC8548輸出的3對時鐘對以驅動內存條上的9片DDR2 SDRAM芯片。對于沒有使用到的時鐘對,可以通過配置MPC8548的內部寄存器DDRCLKDR進行關閉。

在電源設計方面,需要仔細計算VTT電源發生器及其電源平面是否能滿足設計所需要的功耗;需要仔細對VTT, VDDQ, VREF進行去耦濾波;VTT電源平面應該和內存條緊緊相鄰;VREF走線寬度建議為20~25mil并和同層的其他電源或信號有至少20mil的間距,VREF必須能跟隨VDDQ的變化,建議VREF通過電阻分壓網絡從VDDQ直接得到,分壓電阻精度要求為1%;

設計時,還需要仔細考慮信號時序的要求。數據組信號的時序需要參考本小組的MDQS/MDQS#信號,并利用這對差分對的交叉點采樣;地址和命令組信號的時序需要參考對應的時鐘組信號,并利用其上升沿采樣。對于DDR2 SDRAM,建立時間和保持時間需要考慮由于信號邊沿不單調造成的時序降額,計算公式如下:

tSETUP = tSETUP(base) + tSETUP(derating)

tHOLD = tHOLD(base) + tHOLD(derating)

其中,tSETUP和tHOLD是總的建立時間和保持時間要求;tSETUP(base)和tHOLD(base)是從芯片文檔能直接得到的建立時間和保持時間的基本要求;tSETUP(derating)和tHOLD(derating)是根據信號及其參考時鐘的真實爬升速率查表得出的降額值,該表格可以從芯片文檔得到。

這種查表計算降額值的方法,將造成很大的工作量。在實際設計中,一般是利用Hyperlynx等仿真軟件直接得到降額值,從而確定信號的時序裕量。特別需要注意的是地址組,由于地址組信號的負載數目一般都比相應的時鐘信號多,因此需考慮負載對時序造成的影響。

結語

存儲芯片在電子產品中扮演著重要的角色,其性能的高低直接決定著產品的性能。相比DDR SDRAM,DDR2 SDRAM在多方面進行了技術提升,其必將在電子產品市場中發揮越來越重要的作用。

上拉電阻相關文章:上拉電阻原理

評論