嵌入式系統中IP協議用ASIC器件電路設計

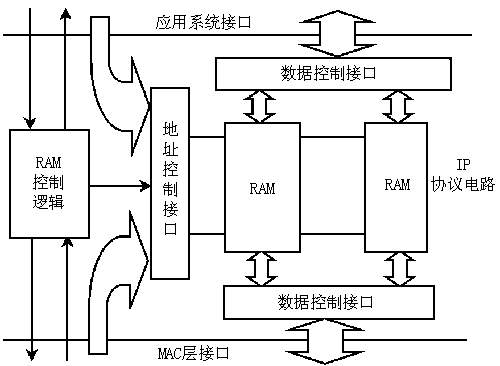

本文設計的IP協議硬件中,采取了上述兩種方式綜合的方法:在IP內設置相應數量RAM模塊,這個RAM模塊不僅是IP協議的數據RAM,同時也是應用系統和MAC層的通信緩沖區。通過握手線與微處理器和MAC層器件連接,握手線中的時鐘信號控制IP協議器件中發送或接收流水線的工作節拍,使整個協議處理實現了并行操作。電路模塊如圖3所示。

本文引用地址:http://www.czjhyjcfj.com/article/83141.htm

圖 3 RAM控制邏輯

三、 流水線方式對電路延遲均勻要求的分析

硬件實現IP協議的特點是協議操作并行,所有協議操作的基本內容完全按照協議的執行內容并行完成。例如發送數據過程中數據的操作如下:

讀入1字節-數據處理-發送1字節

讀入1字節-數據處理-發送1字節

讀入1字節-數據處理-發送1字節

……

為實現上述操作,除了需要使用外部觸發信號作為統一時鐘外,各部分電路延遲的誤差還要受到相應的限制。

IP協議的操作,就是對要傳送的數據報進行相應處理,因此,電路是否正常由數據的穩定性決定。如果電路能在規定的時間內進入穩定狀態,則數據在處理過程中就不會出現問題;否則,數據就會發生不確定性的變化,這種情況就叫作硬件電路的非正常操作結果。出現非正常操作結果的IP協議器件是不穩定的。

影響IP協議器件穩定性的因素是各級電路操作時間長度和觸發時鐘周期。從圖4中可以看出,各級電路的操作時間長度必須小于觸發信號周期,也就是說,必須在一個觸發周期內完成本級電路的所有操作。根據有限狀態機和時序邏輯電路理論可知,各級處理電路都必須是同步時序邏輯電路。另外,各級電路的操作時間長度取決于電路的級聯層數和每級的時間延遲。由此可知,要保證IP協議器件工作穩定,必須同時滿足如下2個條件:

(1) 各級模塊電路處理時間必須小于最小觸發周期;

(2) 各級模塊電路內部延遲能滿足處理時間要求。

作為硬件電路,其處理速度實際上就是數據在邏輯電路中的傳輸速度,因此,可以通過計算數據傳輸經過邏輯門的最大時間延遲,確定每級邏輯模塊電路的工作時間。

在IP協議流水線操作中,設外部觸發時鐘周期為TCLK,各模塊電路的傳輸延遲時間為ti,采用MOS器件的ASIC電路邊沿動作時間均為tp,各模塊內部傳輸經過N級電路,其中每一級的延遲為Δti,則每個模塊電路的總延遲為

ti=NΔti

為保證器件工作穩定,需要有

TCLK>ti=NΔti

結束語

嵌入IP協議的微處理器或單片機系統是嵌入式網絡技術應用的基本技術[2],但工業設備采用軟件嵌入IP協議存在無法并行處理或成本過高的缺點。本文針對工業設備對IP協議需要所設計的IP協議專用器件克服了這些不足,為工業設備提供了實用的、具有較高性能價格比的網絡技術。任何數字化工業設備,都可以使用這個IP協議器件直接連接到基于IP的網絡。

硬件實現的IP協議,其并行工作的數字電路系統必須保證數據處理的穩定性。根據有限狀態機和時序邏輯電路理論,實現并行工作的各級處理電路都必須是同步時序邏輯電路。

使用ASCI技術設計IP協議屬于硬件,是并行操作實現IP協議技術,不僅IP協議的執行不受軟件和系統中斷干擾,還具有一定的IP協議層抗干擾能力。由于ASIC實現的IP協議是一個專用數字硬件電路,只需要通過相應的控制信號就可以實現IP協議的功能,具有比較高的性能價格比。MES

參考文獻

1 Douglas E C,David L S.Internetworking With TCP/IP Vol Ⅰ:Principles,Protocols and Architecture.Second Edition.Department of Computer Science Purdue U

2 Gary R W,W Richard S.TCP/IP Illustrated,volume 2:The Implementation.Addison Wesley Publishing Company,1995

tcp/ip相關文章:tcp/ip是什么

評論