基于FPGA的數(shù)字視頻轉(zhuǎn)換接口的設計與實現(xiàn)

引言

本文引用地址:http://www.czjhyjcfj.com/article/79677.htm本文從實際應用的角度出發(fā),采用FPGA作為主控芯片,設計了一款數(shù)字視頻接口轉(zhuǎn)換設備,該設備針對于MT9M111這款數(shù)字圖像傳感器產(chǎn)生的ITU-R BT.656格式數(shù)據(jù)進行采集、色彩空間變換、分辨率轉(zhuǎn)換等操作,完成了從ITU-R BT.656格式數(shù)據(jù)到DVI格式數(shù)據(jù)的轉(zhuǎn)換,使得MT9M111數(shù)字圖像傳感器的BT656數(shù)據(jù)格式圖像能夠以1280×960(60Hz)和1280×1024(60Hz)兩種顯示格式在DVI-I接口的顯示器上顯示,并且還具有圖像靜止功能,在系統(tǒng)空閑時的待機狀態(tài)實現(xiàn)了整機的低功耗,適用于使用移動設備的工業(yè)現(xiàn)場。

整體方案設計

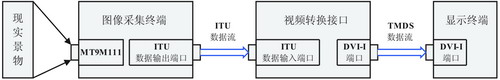

現(xiàn)實景物的采集與顯示過程如圖1所示。圖像傳感器MT9M111采集到現(xiàn)實景物后,將生成的ITU-R BT.656數(shù)據(jù)流由ITU數(shù)據(jù)輸出端口發(fā)送給視頻轉(zhuǎn)換接口。視頻轉(zhuǎn)換接口將ITU數(shù)據(jù)輸入端口送來的ITU-R BT.656數(shù)據(jù)流轉(zhuǎn)換成TMDS數(shù)據(jù)流發(fā)送,通過DVI-I端口發(fā)送給顯示終端顯示。本設計方案中,MT9M111輸出圖像的分辨率為1280×960。

圖1 系統(tǒng)采集與顯示過程

在現(xiàn)實景物的采集與顯示過程中,視頻轉(zhuǎn)換接口功能的實現(xiàn)通過以下步驟來完成:

1) 對收到的ITU-R BT.ITU656數(shù)據(jù)流解交織;

2) 對解交織后的數(shù)據(jù)流進行色彩空間轉(zhuǎn)換;

3) 將轉(zhuǎn)換后的每個像素的RGB值寫入存儲器中;

4) 從存儲器中讀出像素的RGB值,并將其轉(zhuǎn)換成TMDS碼元序列;

5) 從存儲器中讀出像素的RGB值,并將其轉(zhuǎn)換成VGA模擬信號值。

硬件構(gòu)架設計

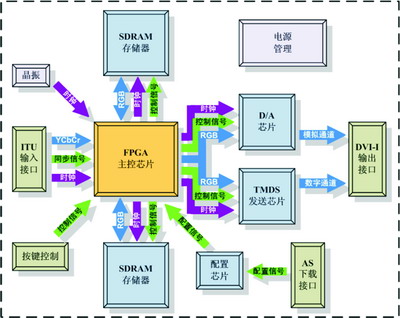

系統(tǒng)的硬件構(gòu)架框圖如圖2所示。圖像傳感器輸出的ITU信號(包括YCbCr數(shù)據(jù)流、行場同步信號和像素時鐘)經(jīng)ITU輸入接口送入FPGA主控芯片。FPGA主控芯片對ITU信號進行解交織和色彩空間轉(zhuǎn)換,再將轉(zhuǎn)換后的每個像素的RGB值寫入SDRAM存儲器。再由FPGA主控芯片按照輸出分辨率的要求從SDRAM存儲器中讀出像素的RGB值,并按照VGA的時序標準,將像素的RGB值發(fā)送給TMDS發(fā)送芯片和D/A芯片,由TMDS發(fā)送芯片提供視頻數(shù)據(jù)的數(shù)字通道,由D/A芯片提供視頻數(shù)據(jù)的模擬通道,共同匯集到DVI-I輸出接口,傳送到數(shù)字顯示器或模擬顯示器上顯示。

圖2 硬件構(gòu)架框圖

輸出圖像的分辨率要求FPGA與TMDS發(fā)送芯片之間傳送數(shù)據(jù)的帶寬在100M(像素/秒)以上,因此要求FPGA的速度足夠快。同時由于FPGA與外圍器件之間的互聯(lián)比較多,因此要求FPGA的引腳數(shù)足夠多。同時由于晶振提供的時鐘頻率為50MHz,滿足不了100M以上的傳輸速度,因此需要FPGA內(nèi)部帶有鎖相環(huán)。另外,為了實現(xiàn)系統(tǒng)脫機工作,要求FPGA支持配置芯片。最后,考慮到系統(tǒng)占用的面積和以后版本的升級,要求FPGA的內(nèi)部資源盡量豐富。為此,系統(tǒng)最終選用了Altera公司Cyclone系列FPGA。

考慮到視頻數(shù)據(jù)的存儲和顯示是同時進行的,而SDRAM存儲器是單端口器件,數(shù)據(jù)的寫入和讀出不能同時進行,故需要兩塊SDRAM同時進行乒乓操作來完成數(shù)據(jù)的連續(xù)讀寫。最終選用了MICron公司的型號為MT48LC2M32B2TG-6的SDRAM存儲器;TMDS發(fā)送芯片選用的是Silicon Image公司的SiI164CT64型號。由于輸出圖像的分辨率要求FPGA與TMDS發(fā)送芯片之間傳送數(shù)據(jù)的帶寬在100M以上,這一數(shù)據(jù)流同時又要送入D/A芯片完成數(shù)模轉(zhuǎn)換,因此要求D/A芯片的轉(zhuǎn)換速率在100MHz以上。同時由于R、G、B的數(shù)據(jù)寬度都為8位,因此需要選用專用的圖像D/A芯片,它需要具有R、G、B三路數(shù)據(jù)通道,每路的寬度至少為8位。根據(jù)以上要求,系統(tǒng)最終選定CSEMIC公司的CSV7123型號的圖像D/A芯片。

FPGA功能設計

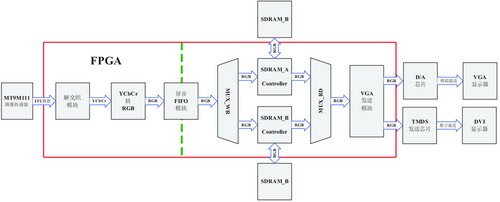

FPGA作為系統(tǒng)的主控芯片,是軟件設計的核心。根據(jù)整體方案的設計思路,F(xiàn)PGA主控芯片的工作過程為:首先接收由圖像傳感器送來的ITU-R BT.656格式的視頻數(shù)據(jù)流,經(jīng)過解交織操作,將像素數(shù)據(jù)流中交織在一起的串行YCbCr值解成獨立的并行YCbCr值。然后對解交織的YCbCr值進行色彩空間轉(zhuǎn)換,轉(zhuǎn)換成對應的RGB值。接著將此RGB值存入一塊SDRAM存儲器。與此同時,從另一塊SDRAM存儲器中讀出像素的RGB值,并發(fā)送給TMDS發(fā)送芯片和D/A芯片,經(jīng)過數(shù)字通道和模擬通道后,傳送到DVI顯示器或VGA顯示器上顯示。根據(jù)FPGA主控芯片的工作過程,設計的軟件功能框圖如圖3所示。

圖3 軟件功能框圖

圖3中FPGA內(nèi)部的工作時鐘有兩個,以圖中的虛線為界,虛線左側(cè)部分使用的時鐘為圖像傳感器的54MHz像素時鐘;虛線右側(cè)使用的時鐘是經(jīng)過鎖相環(huán)將晶振的50MHz時鐘倍頻成108MHz以后的時鐘,其中108MHz的時鐘是由輸出圖像的分辨率所決定的。兩個時鐘域通過異步FIFO相連。整個系統(tǒng)共分成6個模塊:解交織模塊、YCbCr轉(zhuǎn)RGB模塊、異步FIFO模塊、乒乓操作模塊、SDRAM控制器模塊和VGA發(fā)送模塊。此外,系統(tǒng)還可實現(xiàn)圖像靜止、系統(tǒng)待機、模式選擇等功能。

圖像顯示效果

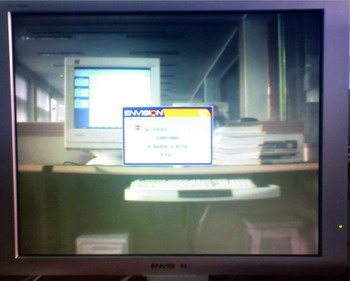

圖4是輸出圖像分辨率為1280×960模式下的顯示效果,圖中顯示器檢測到的視頻圖像分辨率為1280×960

圖4 1280×960模式下的顯示效果

評論