基于ARM核的音頻解碼器單芯片系統研究

摘 要: 簡要介紹Cirrus Logic公司的嵌入式處理器產品EP7209的結構、功能、接口特性等,并給出基于EP7209所能構建的最大系統。對使用EP7209構建嵌入式系統有一定參考價值,也有助于了解ARM核。

本文引用地址:http://www.czjhyjcfj.com/article/264817.htm關鍵詞:嵌入式處理器 嵌入式系統 ARM核

引 言

EP7209是世界上第一片既支持流行的MP3標準,也支持諸如Microsoft Audio等快速涌現的互聯網音頻壓縮標準的數字音頻解碼器片上系統。EP7209在74MHz下運行時其性能與基于100MHz英特爾奔騰芯片的個人計算機相同,且消耗的功率特別小:在2.5V電壓下,功耗不足170mW。它的ARM核提供了一個優秀的數字信號處理器所能夠提供的處理能力,因此,互聯網音頻處理僅占用了該芯片50%的處理能力。這給嵌入式系統的設計人員留下了高達25MIPS(百萬條指令每秒)的處理能力用于實現其它功能。本文著重討論 EP7209的結構、功能、接口特性等及其在嵌入式系統中的應用。

一、功能框圖及功能塊描述

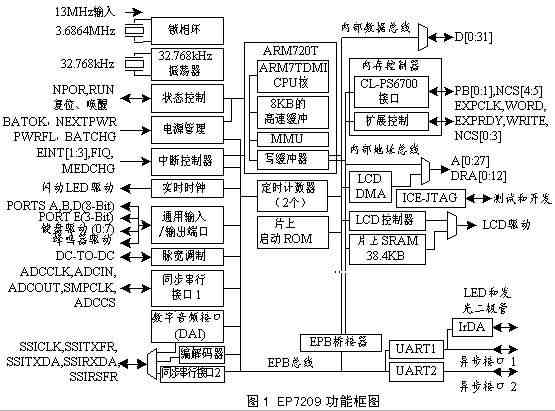

圖1是EP7209的功能框圖。由圖1可知EP7209含有如下功能塊。

(1)ARM720T處理器含有如下功能子塊:

① ARM7TDMI CPU核。該CPU核支持Thumb指令集、核調試、增強的乘法器、JTAG以及嵌入式ICE。它的時鐘速率可編程為18MHz、36MHz、49MHz、74MHz。

② 內存管理單元(MMU)與ARM710核兼容,并增加了對Windows CE的支持。該內存管理單元提供了地址轉換和一個有64個項的轉換旁路緩沖器。

③ 提供了8KB的單一的指令和數據高速緩沖存儲器以及一個四路相聯高速緩沖存儲器控制器。

④ 寫緩沖器。

(2)38400字節的片上SRAM,可以在LCD控制器和通用應用之間共享。

(3)內存可以和高達6個獨立的擴展段接口,每個擴展段有256MB,且等待狀態可編程。

(4)27位的通用I/O,可以多路復用,以在需要時提供額外的功能。

(5)數字音頻接口(DAI)可以直接與CD音質的DAC和編解碼器相連。

(6)中斷控制器。

(7)先進的系統狀態控制及電源管理。

(8)2個16550A兼容的全雙工UART,含16字節的發送及接收FIFO。

(9)SIR協議紅外線數據編解碼器,速率最高達115.2kbps。

(10)LCD控制器,16級灰度,可編程為1、2或4位每像素。

(11)片上的啟動ROM,已固化了用于串行加載的啟動代碼。

(12)2個16位的通用定時計數器。

(13)1個32位的實時時鐘(RTC)和比較器。

(14)2個同步串行接口,用于諸如ADC等Microwire或SPI外圍器件。一個接口支持主模式和從模式,另一個僅支持主模式。

(15)完全的JTAG邊界掃描和嵌入式ICE支持。

(16)2個可編程的脈沖寬度調制接口。

(17)1個用于和1或2個Cirrus Logic CL-PS6700 PC卡控制器器件相連的接口,可支持2個PC卡插槽。

(18)振蕩器和鎖相環,用于由外部的3.6864 MHz的晶振產生內核所需要的18.432MHz、36.864 MHz、 49.152MHz或73.728MHz的時鐘。此外還有一個外部時鐘輸入端(在13MHz模式下使用)。

(19)一個低功耗的32.768kHz的振蕩器,用于產生實時時鐘所需要的1Hz時鐘。

所有的外部存儲器和外圍器件都應連接到32位的數據總線D[0:31]上,并應使用28位的地址總線A[0:27]和其它控制信號。

二、基本工作原理

EP7209的核心邏輯功能是建立在一個ARM720T嵌入式處理器之上的。對EP7209的設計,以低功耗為目的進行了優化,并使用完全靜態的 0.25μm的CMOS制造工藝。低功耗的思想同樣體現在狀態設計、時鐘使用的方式上。下面將有選擇地介紹EP7209的工作原理。

1.CPU內核

ARM720T由一個ARM7TDMI 32位RISC處理器、一個單一的高速緩沖和一個存儲器管理單元(MMU)所構成。8KB的高速緩沖有一個四個項的相聯寄存器,并被組織成512線四字 (4×512×4字節)。高速緩沖直接與ATM7TDMI相連,因而高速緩沖來自CPU的虛擬地址。當所需的虛擬地址不在高速緩沖中時,由MMU將虛擬地址轉換為物理地址。一個64個項的轉換旁路緩沖器(TLB)被用來加速地址轉換過程,并減少頁表讀取所需的總線傳送。僅通過轉換高速緩沖中未存儲的地址,MMU就能夠節約功率。

2.狀態控制

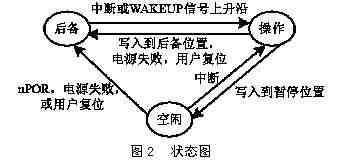

EP7209支持如下的電源管理狀態:操作、空閑和后備(節能),如圖 2所示。正常的程序執行狀態為操作狀態。這是一個完全性能狀態,時鐘和外圍器件都被使能。除了CPU時鐘被暫停外,空閑狀態與操作狀態是一樣的。一個中斷或喚醒將使空閑狀態返回到操作狀態。后備狀態下功耗最小,選擇此模式會關閉主振蕩器,只對實時時鐘和相關邏輯提供電源。當EP7209處于后備狀態時,為保證系統能夠正常喚醒,所有電源和地引腳仍然與電源和地相連是非常重要的。后備狀態唯一能夠變遷到的狀態是操作狀態。

3.復 位

EP7209有三個異步復位信號:nPOR、nPWRFL和nURESET。如它們中的任一個有效,系統復位將由內部產生。除了RTC數據和匹配寄存器外,所有的EP7209內部寄存器都將被復位。為了使系統時間在用戶復位或電源失敗的狀況下得以保持,RTC數據和匹配寄存器僅由nPOR引起的復位所清除。

任何復位都將復位CPU,并在EP7209返回操作狀態時使CPU從復位矢量處開始執行程序。

4. 時 鐘

EP7209有兩個時鐘模式:外部時鐘輸入和片上PLL。時鐘源的選取是由端口E的第2腳(PE[2])的一個陷阱選項來實現的。如果PE[2]在 nPOR的上升沿處為高(例如上電時),外部時鐘模式被選取;如果PE[2]為低,那么,片上PLL模式被選取。上電以后,PE[2]可用作通用輸入輸出端口。

EP7209器件有幾個獨立的邏輯部分,每一個都有自己的時鐘頻率要求。當EP7209處于外部時鐘模式時,外圍器件的真實頻率將不同于PLL模式時的頻率。

5. 中斷處理

在程序的執行期間,當一個不可預測事件 (如中斷或存儲器錯誤) 發生時,通常要產生一個例外。當這些例外在同一時間發生時,將由固定優先權服務體系決定其被處理的次序。表1顯示了所有例外的優先權次序。

晶振相關文章:晶振原理 矢量控制相關文章:矢量控制原理 鎖相環相關文章:鎖相環原理

評論