便攜式設備中的電源效率

高PSRR帶隙電壓參考電路

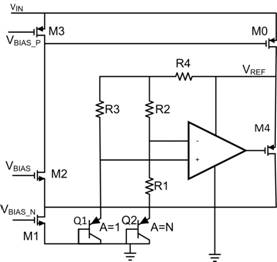

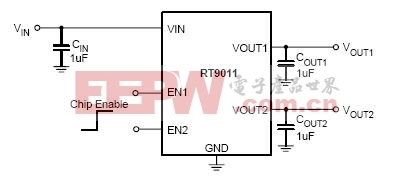

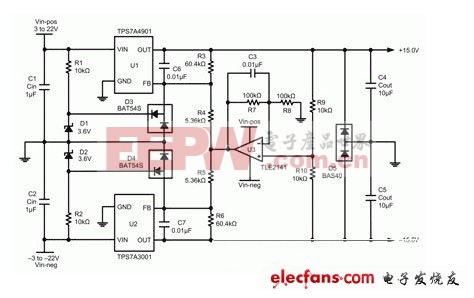

本文引用地址:http://www.czjhyjcfj.com/article/264576.htm由于上述傳統電壓參考架構的所有缺點,我們建議采用改進的電壓參考,它是帶隙電壓參考與低壓降穩壓器的整合解決方案(圖6)。

圖6.帶隙電壓參考結合低壓降穩壓器的方框圖

該示例中的輸出電壓可由公式8確定:

VREF節點既是帶隙參考的輸出節點,同時也是帶隙核心電路的電源線。這有助于我們通過 LDO保護帶隙核心電路免受電源電壓紋波影響。

要獲得小靜態電流,電阻器 R1、R2、R3和R4的值就會比較大,推薦電路的電阻為8MΩ。這可使通過 Q1和Q2的電流降低至 40nA。推薦架構的整體靜態電流為250nA。除此之外,我們還可采用一款靜態電流為100nA的偏置電流電源。

偏置電流電路

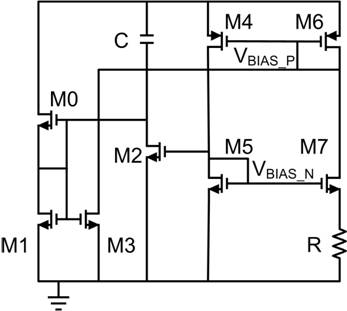

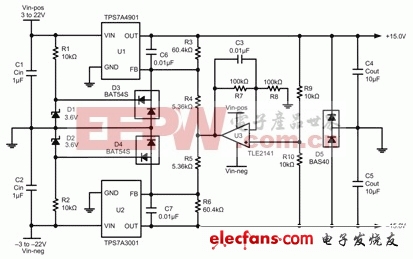

所推薦的偏置電流電路基于一種著名的電路結構(如圖7所示),在參考文獻5[5]中有詳細介紹。

在該電路中,兩個N型晶體管M5和M7構成第一個增益為S7/S5 的電流鏡,而兩個P型晶體管M4和M6 則構成第二個增益為S4/S6 的電流鏡,其中S4、S5、S6和S7是相應晶體管的面積。

偏置發生器通常不需要特別啟動電路,這可減少靜態電流和占用面積。如果電流足夠小,電阻R 就可以忽略。由M5/M7和M4/M6構成的兩個電流鏡可互連成一個閉環。

該環路增益大于單位增益,因此兩個分支中的電流都會增大,直至達到均衡為止。這將由電阻R的壓降定義,可表示為公式9:

圖7.具有動態啟動電流的偏置生成器

要加快啟動速度并避免可能的漏電影響,可使用一款附加啟動電路。晶體管M0 可作為具有極大電阻的橫向雙極性 NPN晶體管使用,其可最大限度地降低啟動電流。電容器 C 不僅可在電路加電時提供快速瞬態啟動,而且還可防止啟動電路發生振蕩。在啟動之后,電路由晶體管M2阻斷。偏置模塊的偏置電流是40nA。總流耗是 80nA。

驗證結果

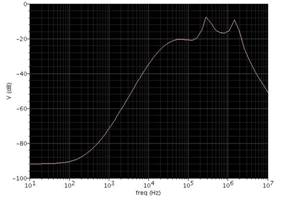

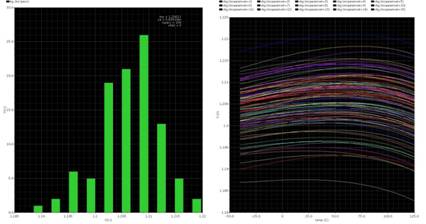

所推薦帶隙參考不僅可用于超低噪聲、高PSRR的低壓降穩壓器,而且還可采用CMOS 9T5V 技術實施。PSRR值如圖8所示,輸出電壓精度的蒙特卡洛溫度變化仿真結果如圖9所示。測量結果請參見表1。

圖8.電壓參考源的PSRR

圖9.輸出電壓精度

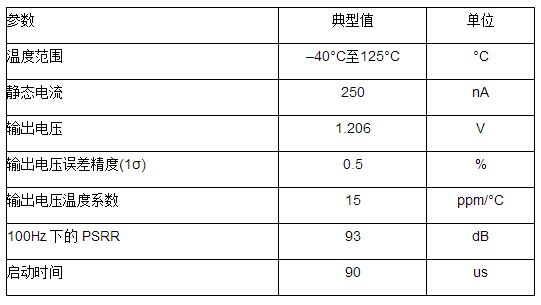

表1.測量數據

總結

我們不僅介紹了采用 CMOS9T5V 0.18µm工藝實施的、高PSRR 的極低功耗帶隙電壓參考,而且還詳細介紹了最大限度降低功耗和最大限度提高PSRR的設計條件。將帶隙電壓參考與低壓降穩壓器相結合,可在100Hz下獲得93dB的高PSRR。該電路的最大靜態電流僅為250nA,是超低功耗應用最具吸引力的選擇。

參考文獻

J. Guo和K. N. Leung,《采用 90 納米 CMOS工藝技術實施的、無輸出電容器的小型 6uWLDO》,摘自《IEEE固態電路雜志》2010年9月第 48卷第 9 號;

Blakiewicz, G.,《支持更快時間響應的CMOS低壓降穩壓器》,摘自《2011年第18屆國際大會會議記錄 — 集成電路與系統混合設計 (MIXDES)》2011年6月16 ~ 18 日第 ××卷第 ×× 號的第 279 頁 ~ 282 頁;

P. Hazucha、T. Karnik、B. A. Bloecher、C. Parsons、D. Finan 和 S. Borkar,《支持超快負載調節的小型線性穩壓器》,摘自《IEEE固態電路雜志》2005 年 4 月第 45 卷第 4 號;

S. Strik,《帶隙電壓參考:誤差及其最小化方法》,摘自《BEC 2006會議記錄》2006年10月2日第 123 頁 ~ 126頁;

E. Vittoz 與 J. Fellrath,《基于弱反向工作的CMOS模擬集成電路》,摘自《IEEE固態電路雜志》1977年6月SC-12卷第 3 號;

如欲了解有關LDO的更多詳情,敬請訪問:www.ti.com/ldo-ca。

電容器相關文章:電容器原理

評論