時鐘采樣系統最大限度減少抖動

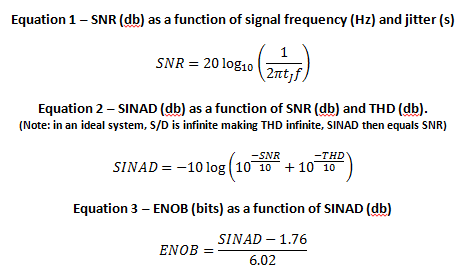

很多人都知道,抖動(這是時鐘邊沿不確定性)是不好的現象,其不僅可導致噪聲增加,而且還會降低數據轉換器的有效位數 (ENOB)。

本文引用地址:http://www.czjhyjcfj.com/article/263956.htm

例如,如果系統需要 100MHz 14(最小值)位的 ENOB,我們就需要抖動小于 80 飛秒的時鐘!這可通過假設一個無失真的理想系統進行計算,讓 SINAD 和 SNR 數值相等(見公式 2)。

接下來,使 ENOB 等于 14,我們可在大約 86db 下計算出最小 SNR。將結果帶入公式 1,計算出大約為 80fs 的 tJ 值。

在數字信號處理過程中,采樣時鐘與處理時鐘之間需要有一定關聯。也就是說,無論是在十分之一速率下還是在全速率下采樣,樣片都必須在其速率的倍數下進行處理,而且要相位一致。這就需要一個“主”時鐘,其可用來衍生系統中的所有其它時鐘。

您可使用溫度補償晶體振蕩器 (TCXO) 和低相位噪聲 PLL 實現這一點,可將主時鐘顯著增加至更高的頻率。然后,您可對該最新高頻率時鐘進行下分頻,以提供都與主時鐘相關聯的剩余系統時鐘。這樣,采樣時鐘以及各種數字處理時鐘都相互具有關聯性。

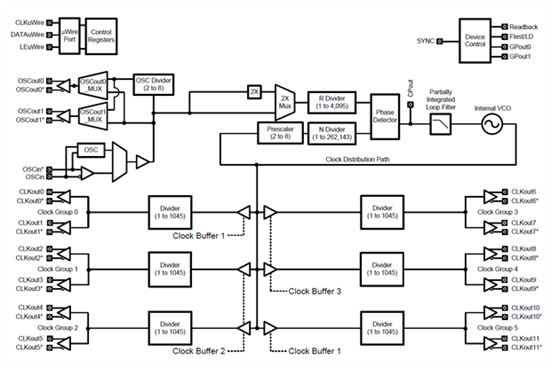

現在有很多時鐘解決方案,但很多都需要時鐘緩沖器或其它時鐘分配方法,其可降低整體抖動性能。您可使用如 LMK03806 等一款器件來克服這個問題,其在同一器件中整合了所有主時鐘發生器和時鐘分配功能(帶驅動器),如圖 1 所示。該器件可在 300MHz 下運行的同時,具有不足 50fs 的 RMS 抖動(1.875MHz 至 20MHz)。此外,您還可通過對輸出進行編程來支持 LVDS、LVPECL 或 LVCMOS 并對其進行同步,以獲得共用上升沿。

圖 1 — LMK03806(具有時鐘發生器、時鐘分頻器和驅動器)的方框圖

因此,您下次設計采樣系統時,別忘了考慮時鐘抖動性能,因為這會影響整體動態范圍。

可控硅相關文章:可控硅工作原理

比較器相關文章:比較器工作原理

負離子發生器相關文章:負離子發生器原理 分頻器相關文章:分頻器原理 離子色譜儀相關文章:離子色譜儀原理

評論