理解JESD204B協議

在使用我們的最新模數轉換器 (ADC) 和數模轉換器 (DAC) 設計系統時,我已知道了很多有關 JESD204B 接口標準的信息,這些器件使用該協議與 FPGA 通信。此外,我還在 E2E 上的該欄目下閱讀了各種技術文章及其它博客文章,明白了為什么 JESD204B 是 LVDS 和 CMOS 接口的后續產品。

本文引用地址:http://www.czjhyjcfj.com/article/263955.htm有一個沒有深入討論的主題就是解決 ADC 至 FPGA 和 FPGA 至 DAC 鏈路問題的協議部分,這兩種鏈路本來就是相同的 TX 至 RX 系統。作為一名應用工程師,我所需要的就是了解其中的細微差別,這樣才能充分利用 JESD204B 通過現有 LVDS 和 CMOS 接口提供的優勢。

有了 JESD204B,您無需再:

使用數據接口時鐘(嵌入在比特流中)

擔心信道偏移(信道對齊可修復該問題)

使用大量 I/O(高速串行解串器實現高吞吐量)

擔心用于同步多種 IC 的復雜方法(子類 1 和 2)

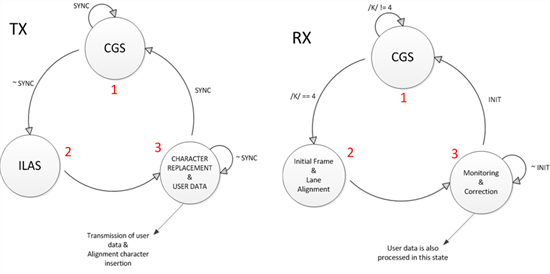

我們來考慮一種由 ADC 等數字源向 FPGA 發送數字數據的簡單情況。在正確發送或接收數據之前,有幾件事必須要做,如圖 1 所示以及下文所說明的那樣。

圖 1. JESD204B 協議狀態圖

1. 代碼組同步 (CGS) — 不需要接口時鐘,因此 RX 必須將其數位及字邊界與 TX 串行輸出對齊。RX 可向 TX 發送 SYNC 請求,讓其通過所有信道發送一個已知的重復比特序列,本例中每字符每 K 是 K28.5。確切的字符比特序列可在標準中找到。RX 將移動每個信道上的比特數據,直到找到 4 個連續的 K28.5 字符為止。這時,它不僅將知道比特及字邊界,而且已經實現了 CGS。隨后,它會取消對 SYNC 的斷言,而 TX 和 RX 則都會進入下一個狀態:初始信道對齊序列 (ILAS)。

2. ILAS — JESD204B 協議的一個良好特性可實現通過 RX 模塊中的一些 FIFO/緩沖器吸收信道偏移。在實現 CGS 后,TX 可在每個信道上發送已知的字符幀集合,稱為信道對齊序列(以每字符每 R K28.0 開始,以每字符每 A K28.3 結束)。收到對齊序列后,RX 會對數據進行 FIFO 緩沖,直到所有信道都收到完整的對齊序列。由于已經知道了整個序列,因此信道隨后可重新對齊,這樣每個信道上的任何信道偏移都可通過 FIFO 存儲器吸收,而且,信道隨后還可在相同的時間點、在 RX 模塊內釋放該數據。這可緩解為串行解串器信道提供匹配布局的需求,因為信道偏移可通過 FIFO 存儲器吸收。

3. 用戶數據 — 在代碼組同步及信道對齊后,就可正確接收用戶數據。如果在該最后狀態時用戶數據無效,則需要重新啟動本過程,RX 會發送一個 SYNC 請求重新開始該過程。

第一次使用新技術可能會令人生畏。如果您正考慮在下個項目中使用該接口,希望我對 JESD204B 中協議的簡單介紹能幫助您緩解這種不適。

模數轉換器相關文章:模數轉換器工作原理

評論