數字射頻存儲器用GaAs超高速3bit相位體制ADC的設計與實現

1、引言

數字射頻存儲器(DRFM)具有對射頻和微波信號的存儲及再現能力,已發展成為現代電子戰系統和儀器測試系統的重要組成部分。作為DRFM的核心部分,超高速ADC,DAC 的性能直接決定了它處理模擬信號的能力。但是,由于半導體工藝及器件性能的限制,高采樣率、高分辨率的ADC 及DAC 難以實現。由于相位數字化比傳統的幅度數字化有多種優點,且采用相位量化可降低對上述電路的要求,所以含相位體制ADC 及DAC 的DRFM 系統得到廣泛應用。本文利用GaAs MESFET 全離子注入非自對準常規工藝設計了用于3bit 相位體制DRFM 系統的單片超高速相位體制ADC。測試結果表明,電路可在2GHz 時鐘速率下完成采樣、量化,達到1.2Gbp s 的輸出碼流速率,其瞬時帶寬可達150MHz,具備±0.22LSB 的相位精度。

2、電路設計

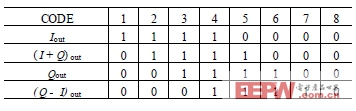

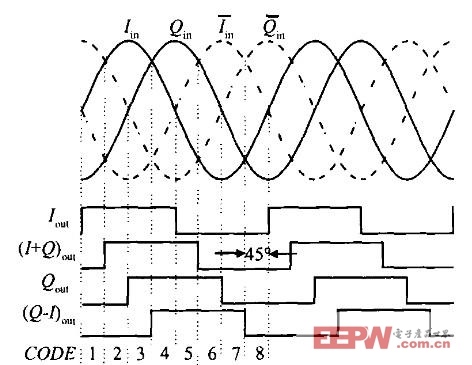

3bit 相位體制ADC的量化對象是輸入信號的相位量,基本功能是將輸入的兩路正交模擬信號轉換為四路含相位信息的數字信號。輸出信號是占空比為1:1、頻率與輸入正交信號同頻 率的方波信號,但每相鄰兩路之間的相位差為45°。3bit 相位體制ADC 的輸入輸出時序關系及真值表分別如圖1、表1 所示。所以,3bit 相位體制ADC 的輸出信號每周期含8 個相位態,電路的轉換速率為輸入模擬信號頻率的8 倍。

表1、輸出真值表

圖1、輸入輸出時序圖

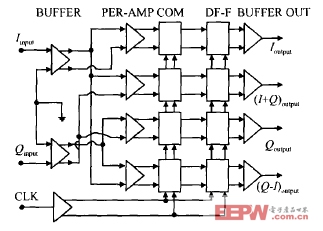

根據3bit 相位體制ADC 的工作原理,設計電路框圖如圖2 所示。

圖2、3bit 相位體制ADC 電路框圖

3bit 相位體制ADC 主要由五部分電路組成:(1)輸入緩沖級。本級電路將輸入的單端模擬正交信號變換為ADC 內部所需的互補信號,并具有一定的放大作用。此外,該級電路還包括將外部的單端時鐘信號變換為內部其他各級電路所需的互補時鐘信號。(2)預放大級。本級 電路根據3bit 相位量化的原理對模擬正交信號及其互補信號按照一定規則兩兩組合,進行差分放大。(3)比較級。本級電路在時鐘作用下,利用正反饋原理對比較器輸入端的模 擬信號進行取樣、量化。(4)觸發鎖存級。本級電路在時鐘的精確控制下,對前級比較級輸出的量化數字值進行觸發鎖存。(5)輸出緩沖級。目的是為了在高速 數字傳輸時能足以驅動ADC 后級的50Ω 負載。電路設計時,已將輸入、輸出端口設計為片內50Ω 匹配,便于高速測試及應用。

功分器相關文章:功分器原理

評論