基于SRAM芯片立體封裝大容量的應(yīng)用

靜態(tài)隨機(jī)存儲(chǔ)器(static RAM),簡(jiǎn)稱(chēng)SRAM。在電子設(shè)備中,常見(jiàn)的存儲(chǔ)器有SRAM(靜態(tài)隨機(jī)訪問(wèn)存儲(chǔ)器)、FLASH(閃速存儲(chǔ)器)、DRAM(動(dòng)態(tài)存儲(chǔ)器)等。其中不同的存儲(chǔ)器有不同的特性,SRAM無(wú)需刷新電路即能保存它內(nèi)部存儲(chǔ)的數(shù)據(jù)。而DRAM每隔一段時(shí)間,要刷新充電一次,否則內(nèi)部的數(shù)據(jù)即會(huì)消失。與SDRAM相比,SRAM不需要時(shí)鐘信號(hào),即可保持?jǐn)?shù)據(jù)不丟失。

本文引用地址:http://www.czjhyjcfj.com/article/234653.htm1、VDMS16M32芯片介紹

VDSR16M32是一款工作電壓3.3V,16Mbit,32位數(shù)據(jù)總線的立體封裝SRAM模塊芯片,由4個(gè)256K x 16bit的SRAM芯片堆疊而成。整個(gè)模塊采用立體封裝堆疊技術(shù),它們之間的互相連接線非常短,寄生電容小。

1.1 芯片的內(nèi)部功能結(jié)構(gòu)和外部引腳

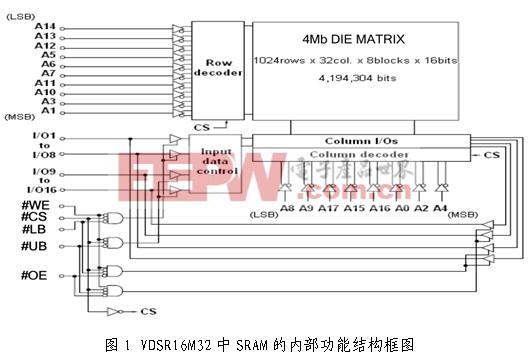

圖1是立體封裝的大容量芯片VDSR16M32中每一片SRAM的內(nèi)部結(jié)構(gòu)和功能框圖,由MEMORY存儲(chǔ)矩形陣列,列譯碼器、行譯碼器、數(shù)據(jù)控制和控制邏輯等部分組成。

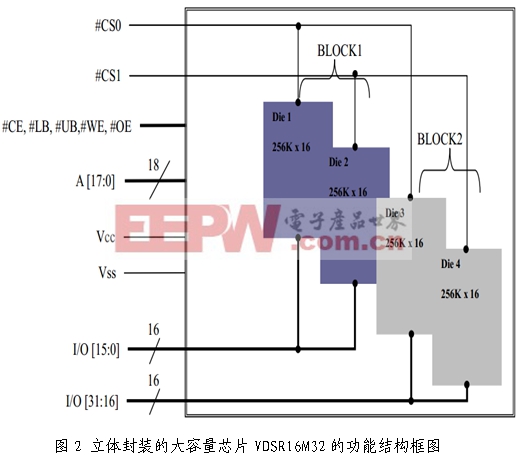

圖2是立體封裝的大容量存儲(chǔ)芯片VDSR16M32的內(nèi)部結(jié)構(gòu)和功能框圖,圖3是VDSR16M32的外部引腳分布圖,其中A【0:17】是地址輸入信號(hào)引腳,#CS0、#CS1是芯片里面BLOCK1和BLOCK2的選擇引腳,#OE是芯片的輸出啟用引腳,#WE是芯片的寫(xiě)入啟用引腳,#LB是低16位的選擇信號(hào),#UB是高16的選擇信號(hào),I/O【0:31】是芯片的數(shù)據(jù)線,其中數(shù)據(jù)線D【0:15】為BLOCK1的數(shù)據(jù)輸入輸出引腳,數(shù)據(jù)線D【16:31】為BLOCK2的數(shù)據(jù)輸入輸出引腳,VCC為電源引腳,VSS為接地引腳。

圖2 立體封裝的大容量芯片VDSR16M32的功能結(jié)構(gòu)框圖

圖3 VDSR16M32的外部引腳分配圖

VDSR16M32的引腳的功能如表1所示:

|

管腳 |

名稱(chēng) |

功能 |

|

#CS0 |

Chip select |

Disables or enables memory die1 and 3 operation |

|

#CS1 |

Chip select |

Disables or enables memory die2 and 4 operation |

|

A0-A17 |

Address |

Row/column 18-bit addresses |

|

#WE |

Write enable |

Enables write operation common to all dies |

|

#OE |

Output enable |

Enables data output common to all dies |

|

#UB |

Upper byte select |

Latches upper bytes addresses common to all dies |

|

#LB |

Lower byte select |

Latches lower bytes addresses common to all dies |

|

I/O1-I/O32 |

Data input/output |

Data I/O1 to I/O16 activated from dies 1 and 2 and Data I/O16 to I/O32 activated from dies 3 and 4 |

|

Vcc/Vss |

Power supply/ground |

Power and ground for the input/output buffers and core logic. |

|

NC |

No connection |

This pin is recommended to be left No Connection on the device. |

| ? |

表1 VDSR16M32的引腳的功能

1.2 芯片的主要特性

1、訪問(wèn)周期:最小12ns;

2、不需要時(shí)鐘信號(hào);

3、兼容TTL電平;

4、數(shù)據(jù)至少可以保持20年;

5、由兩個(gè)256K*32bit的塊組成;

6、由5片4Mbit SRAM 堆疊而成;

7、2個(gè)獨(dú)立片選#CS0,#CS1; 8、

8、工作電壓:3.3V;

9、64腳TSOP封裝。

1.3 芯片的操作

芯片VDSR16M32的工作模式和SRAM差不多,都具有讀寫(xiě)操作模式,關(guān)于芯片VDSR16M32的操作模式的真值表如下圖4所示:

圖4:

VDSR16M32的工作模式的真值表

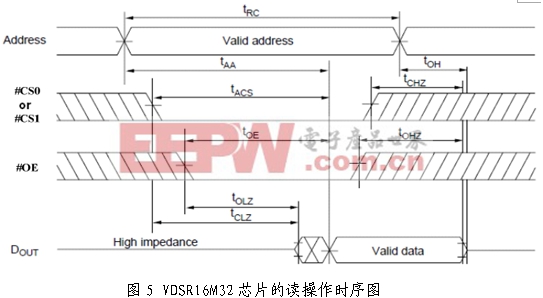

VDSR16M32的讀操作非常簡(jiǎn)單,當(dāng)片選#CS0或者#CS1和輸出啟用引腳#OE都為低電平時(shí),芯片進(jìn)行讀操作,即可從芯片讀出數(shù)據(jù)。VDSR16M32芯片的讀操作時(shí)序圖如圖5所示:

VDSR16M32芯片的讀取操作步驟如下:

1) 通過(guò)地址總線把要讀取的bit的地址傳送到相應(yīng)的讀取地址引腳(這個(gè)時(shí)候/WE 引腳應(yīng)該沒(méi)有激活,所以SRAM 知道它不應(yīng)該執(zhí)行寫(xiě)入操作) 。

2) 激活#CS0或者#CS1選擇該芯片的BLOCK0或者BLOCK1。

3) 激活#OE引腳讓VDSR16M32知道是讀取操作。

第三步之后,要讀取的數(shù)據(jù)就會(huì)傳輸?shù)綌?shù)據(jù)總線。

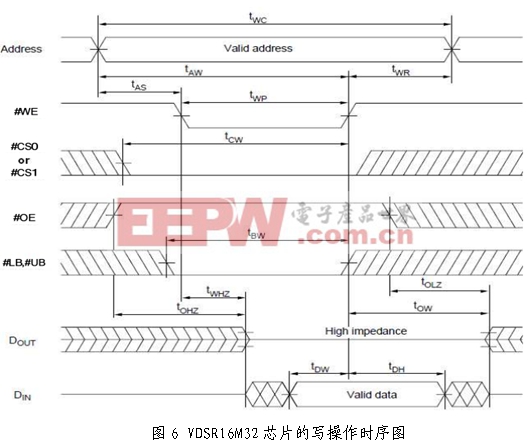

VDSR16M32的寫(xiě)操作同讀操作類(lèi)似,當(dāng)片選#CS0或者#CS1和寫(xiě)入啟用引腳#WE都為低電平時(shí),芯片進(jìn)行寫(xiě)操作,即可寫(xiě)入數(shù)據(jù)到芯片中區(qū)。VDSR16M32芯片的寫(xiě)操作時(shí)序圖如圖6所示:

圖6 VDSR16M32芯片的寫(xiě)操作時(shí)序圖

VDSR16M32芯片的寫(xiě)入操作步驟如下:

1) 通過(guò)地址總線確定要寫(xiě)入信息的位置(確定#OE 引腳沒(méi)有被激活)。

2) 通過(guò)數(shù)據(jù)總線將要寫(xiě)入的數(shù)據(jù)傳輸?shù)絀/O引腳

3) 激活#CS0或者#CS1選擇該芯片的BLOCK0或者BLOCK1。

4) 激活#WE引腳,通知VDSR16M32芯片知道要開(kāi)始寫(xiě)入操作。

經(jīng)過(guò)上面的四個(gè)步驟之后,需要寫(xiě)入的數(shù)據(jù)就已經(jīng)放在了需要寫(xiě)入的地方。

2 VDSR16M32的硬件電路設(shè)計(jì)

2.1 VDSR16M32與S698-T的電路連接

S698-T是珠海歐比特控制工程股份有限公司面向嵌入式控制領(lǐng)域而研制的一款高性能、高可靠的 SoC 芯片,S698-T芯片的存儲(chǔ)器控制器提供了直接訪問(wèn)PROM、I/O空間、SRAM、SDRAM的接口。其中,訪問(wèn)ROM、I/O空間、SRAM時(shí),支持8位、16位和32位三種數(shù)據(jù)總線寬度,其存取時(shí)間參數(shù)可配置。下面以S698-T為例介紹SRAM存儲(chǔ)器為不同位寬時(shí)與MCU的硬件連接方式。

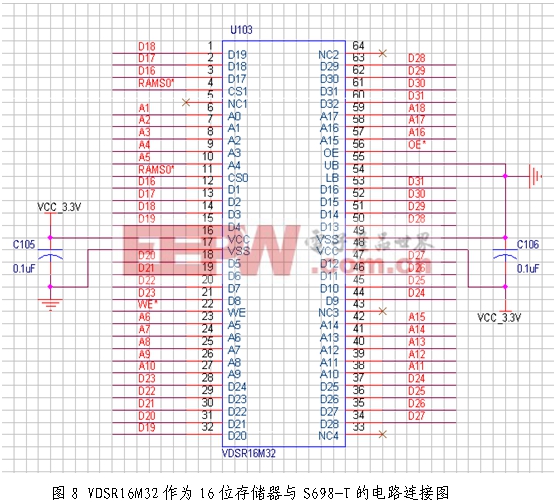

VDSR16M32作為32位存儲(chǔ)器時(shí)與S698-T微處理器的電路連接圖如圖7所示,其中Data【31:0】為微處理器S698-T的32位數(shù)據(jù)線,Address【19:2】是S698-T中28位地址線中的第2位至20位,S698-T在32位總線訪問(wèn)時(shí),地址線從A2開(kāi)始選址。OE*是S698-T的外部存儲(chǔ)器輸出使能信號(hào)低電平有效。WE*是S698-T的外部存儲(chǔ)器寫(xiě)操作使能信號(hào),低電平有效。RAMS0*、RAMS1*是S698-T的SRAM BANK0、BANK1的片選信號(hào),低電平有效。當(dāng)S698-T進(jìn)行32位總線進(jìn)行讀寫(xiě)數(shù)據(jù)操作時(shí),必須同時(shí)選擇片選#CS0和#CS1。

圖7 VDSR16M32作為32位存儲(chǔ)器與S698-T的電路連接圖

VDSR16M32作為16位存儲(chǔ)器時(shí)與S698-T微處理器的電路連接圖如圖8所示,其中Data【31:16】為微處理器S698-T的高16位數(shù)據(jù)線,S698-T是高數(shù)據(jù)位有效。Address【18:1】是S698-T中28位地址線中的第1位至18位,S698-T在16位總線訪問(wèn)時(shí),地址線從A1開(kāi)始選址。OE*是S698-T的外部存儲(chǔ)器輸出使能信號(hào)低電平有效。WE*是S698-T的外部存儲(chǔ)器寫(xiě)操作使能信號(hào),低電平有效。RAMS0*、RAMS1*是S698-T的SRAM BANK0、BANK1的片選信號(hào),低電平有效。當(dāng)S698-T進(jìn)行數(shù)據(jù)操作時(shí),選擇片選#CS0或者#CS1來(lái)選擇操作BLOCK0或者BLOCK1,BLOCK。

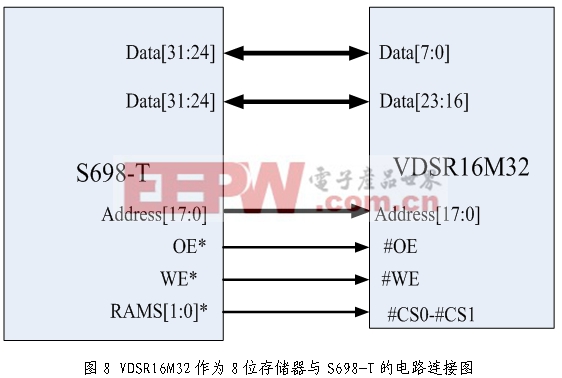

VDSR16M32作為8位數(shù)據(jù)與S698-T連接時(shí),犧牲了芯片的一半性能,所以不推薦這樣使用。VDSR16M32作為8位存儲(chǔ)器時(shí)與S698-T微處理器的電路連接圖如圖9所示,其中Data【31:24】為微處理器S698-T的高8位數(shù)據(jù)線,S698-T是高地址有效。Address【17:0】是S698-T中28位地址線中的低18位,OE*是S698-T的外部存儲(chǔ)器輸出使能信號(hào)低電平有效。WE*是S698-T的外部存儲(chǔ)器寫(xiě)操作使能信號(hào),低電平有效。RAMS【1:0】是S698-T的SRAM BANK0-BANK1的片選信號(hào),低電平有效。

3.結(jié) 語(yǔ)

對(duì)于由靜態(tài)隨機(jī)存儲(chǔ)器(SRAM)堆疊而成的立體封裝的大容量存儲(chǔ)芯片VDSR16M32,由于擁有32位數(shù)據(jù)線,兩個(gè)BLOCK,并且數(shù)據(jù)位可靈活配置,可滿(mǎn)足不同CPU對(duì)位寬的要求。同時(shí)基于SRAM芯片立體封裝存儲(chǔ)器縮短了內(nèi)部信號(hào)連接長(zhǎng)度、減少了寄生效應(yīng),增強(qiáng)了抗干擾能力,可廣泛用于車(chē)輛、衛(wèi)星、飛機(jī)和空間站等對(duì)存儲(chǔ)器條件要求高的地方。

存儲(chǔ)器相關(guān)文章:存儲(chǔ)器原理

評(píng)論