使用PLD應對產品上市時間和設計靈活性的限制

中密度PLD設計的低功耗解決方案

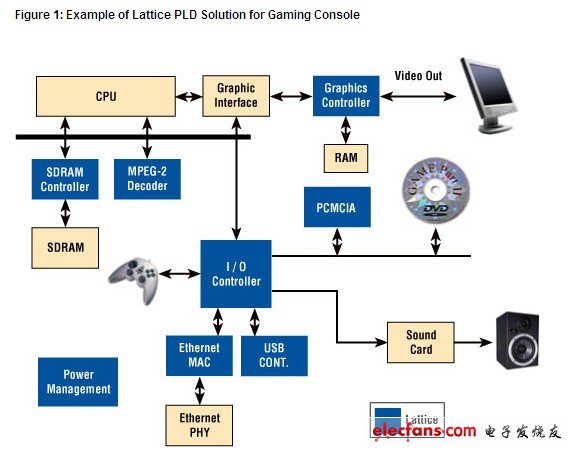

高密度設計需要基于查閱表(LUT)的PLD,例如FPGA或者交叉式PLD器件。這些器件能夠提供更多的嵌入式的功能、更大的存儲器、更高速度、用于時序管理的PLL和DLL、

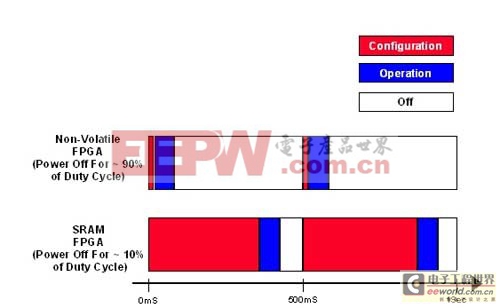

大多數基于LUT的FPGA沒有“零功耗”選擇。但是系統設計者可以在系統的某些工作周期中關閉器件以降低功耗。圖3給出了非易失FPGA的快速電源冷啟動是如何降低總功耗的。上電之后能迅速地獲取邏輯功能的非易失器件對這些應用是理想的。另一方面,基于SRAM的FPGA耗費大部分工作周期用于配置。

圖3:用非易失FPGA在工作周期中降低功耗

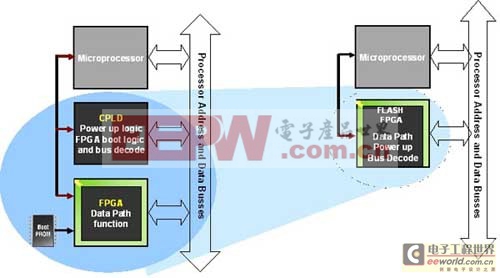

大多數FPGA是基于SRAM的,但是現在已有基于閃存的非易失FPGA。非易失FPGA比基于SRAM的FPGA更具設計優勢。(參見圖4)除了管理電源的功能之外,非易失FPGA的優點還包括:

1. 無需引導PROM,減少了材料清單(BOM)中的器件;

2. 無需位流,提供最高的設計安全性;

3. 實時的系統內可編程性具有調試和更新能力;

4. 無限重構的SRAM FPGA結構。

圖4:非易失FPGA

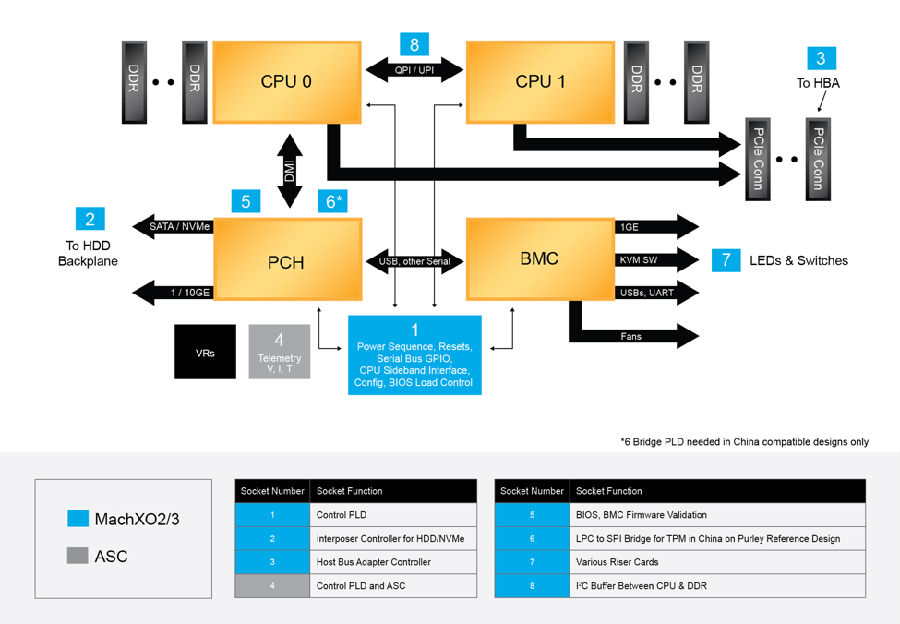

Lattice半導體公司的交叉式可編程器件MachXO就是一個很好的例子。相對傳統CPLD來說,MachXO器件兼有FPGA和CPLD的非易失、低成本、瞬時上電的高性能邏輯解決方案的優點。

本文小結

由于具備上市時間優勢、靈活性、可編程性和低功耗選擇,CPLD和 FPGA在迅速變化的市場中成為廣泛應用的可行的設計解決方案。具多種密度和多樣嵌入功能特色的PLD能為設計提供快速開發周期。正如文中所述,它們能夠針對低功耗和系統的高度整合進行設計優化。隨著工藝的不斷改進,ASIC與 PLD之間的價格也正迅速接近。

評論