基于EDA技術的定向型計算機硬件設計

1 引言

本文引用地址:http://www.czjhyjcfj.com/article/202714.htm隨著計算機技術的迅速發展,計算機系統中使用的硬件部件基本上都采用大規模和超大規模集成電路,這些電路的設計、驗證和測試必須使用先進的工具軟件,使硬件設計逐漸趨于軟件化,加快硬件設計和調試的速度[1],計算機硬件作為一個典型的復雜數字系統,其設計方法發生了根本性的變革。EDA(Electronic Design Automation ,電子設計自動化)技術就是一種自動完成將用軟件的方式設計的電子系統形成集成電子系統或專用芯片的一門新技術[2]。

TDN-CM++實驗裝置是計算機組成原理及系統結構課程的專用實驗箱,但存在硬件結構基本固定、CPU 的各個組成部件全部做好、以驗證型的實驗為主、學生只需按書中要求撥動相應開關就能完成實驗等問題,達不到在整體上把握計算機的基本原理和工作流程的目的,實驗效果不盡人意。

根據目前計算機和集成電路技術的發展現狀,利用TDN-CM++實驗裝置上復雜可編程邏輯器件ispLSI1032芯片,設計一個定向型計算機硬件系統,包括運算器、控制器、存儲器的設計,以達到彌補實驗裝置和實驗項目不足的目的。

2 基于EDA 技術的計算機硬件系統設計過程

設計一臺完整的計算機硬件系統主要經過如下幾個階段:

2.1 確定指令系統

該系統的指令系統如表1所示。指令和數據都采用8位表示。源操作數采用存儲器直接尋址方式,目的操作數采用隱含尋址。

表1 指令系統

2.2 總體結構與數據通路

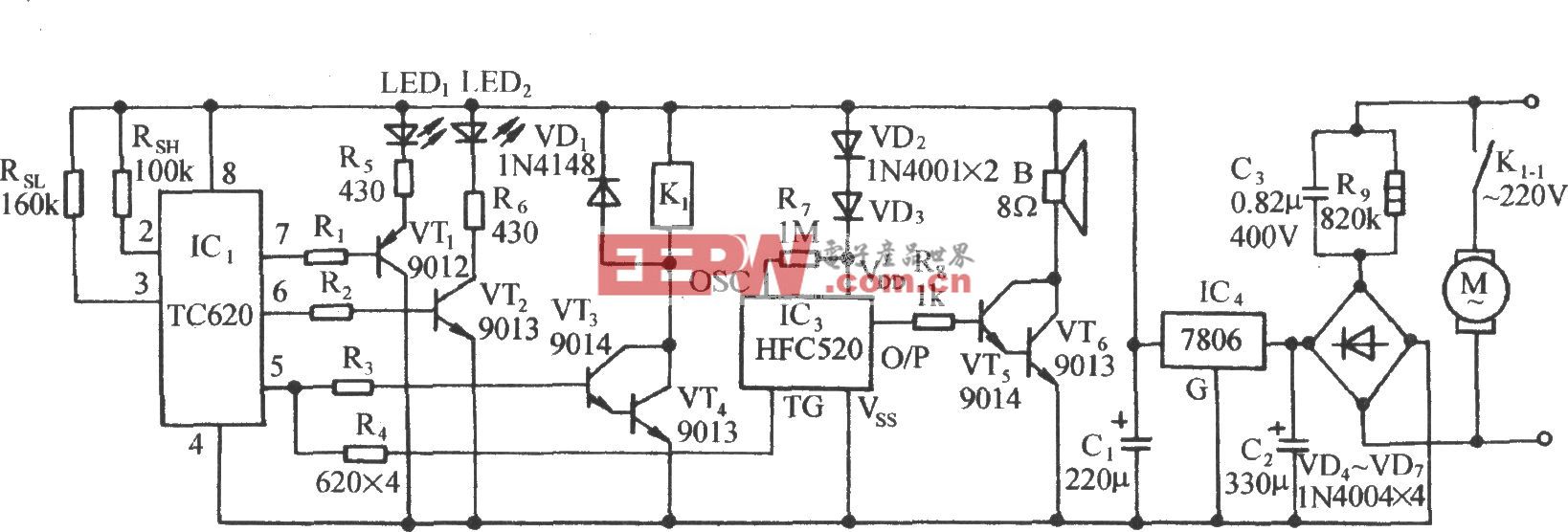

該系統總體結構與數據通路如圖1所示。

圖1 系統總體結構與數據通路圖

2.3 狀態確定

該系統指令周期是6個時鐘周期,前是三個時鐘周期即狀態S0~S2為指令的讀取周期,后3個時鐘周期即S3~S5為指令的執行周期。

2.4 設計指令執行的流程

該系統指令執行流程如表2所示。

表2 指令執行流程

2.5 編程、調試、運行、仿真

編程、編譯、綜合所設計的工程文件,建立測試向量進行功能仿真。將生成的JEDEC 文件下載至實驗儀器的ispLSI 芯片中。按設計的線路圖進行連線。系統連線圖如圖2所示。把程序寫入內存中。調試運行。

圖2 系統連線圖

3 各功能部件的VHDL源程序

3.1 內存ROM功能模塊的VHDL實現

對于圖1中ispLSI 芯片功能圖中內存ROM 16X8的功能采用VHDL實現代碼如下。

rom16x8: process(ce)

begin

if ce='0' then --使能端ce 為邏輯“0”時,才能進行數據的讀取命令。

case addrbus is

when 0000=>

maindata=10100000;

when others=>

maindata=00000000;

end case;

end if; end process rom16x8;

3.2 CPU功能模塊的VHDL實現

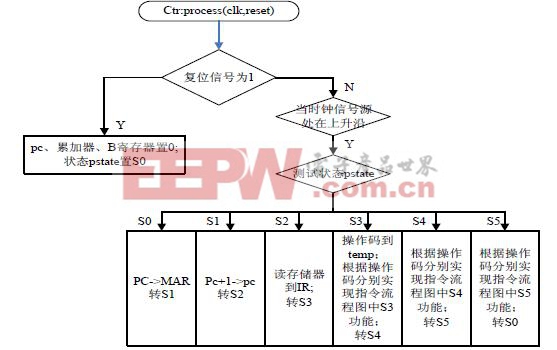

對于圖1 中ispLSI 芯片功能圖中內CPU 功能模塊的VHDL 實現流程如圖3 所示,它是整個模型機的核心。

圖3 CPU 功能模塊VHDL 實現流程

計算機硬件系統的仿真根據ROM的中存放的程序不同,這個模型機完成的操作也就不同,下面將通過建立編寫仿真測試向量,來進行邏輯功能仿真,檢驗設計是否實現了需要完成的功能。 對實現20-6+2運算的工作程序及其在ROM內存映像(起始地址0H)如表3所示:

表3工作程序

進行功能仿真首先需要用ABEL-HDL語言編寫獨立的測試向量文件:

MODULE model

clk,reset,outport,led,wr pin;

Test_vectors ([clk,reset]->[outport,led,wr]) [.x.,1]->[.x.,.x.,.x.];

@REPEAT 100 {[.c.,0]->[.x.,.x.,.x.];} [.x.,1]->[.x.,.x.,.x.];

END

利用上面建立的測試向量文件,其仿真結果如圖4所示。

由仿真波形可以看到在執行OUT 指令時送出20-6+2的運算結果為1C,同時使輸出給OUTPUT DEVICE 的信號led=’0’,wr也由1->0。在執行HLT指令時run 由1->0,模型機停機。這與理論結果完全相符。

圖4 仿真結果

結束語

作者創新點為:提出了在TDN-CM++實驗裝置中的復雜可編程邏輯器件ispLSI1032芯片上,設計定向型計算機硬件系統(包括運算器、控制器、存儲器)的結構、設計方法及具體實現,彌補了TDN-CM++實驗裝置的不足,為進一步理解計算機原理和組成以及系統結構方面的知識創造了條件,為嵌入式系統等的應用打好基礎。

評論