從VHDL代碼到真實硬件:設計有限狀態機

學習如何通過創建一個4位二進制計數器,在VHDL中實現有限狀態機。編譯后,它將在連接到帶有輸入開關和LED顯示器的自定義PCB的Altera CPLD開發板上運行。

本文引用地址:http://www.czjhyjcfj.com/article/202409/462551.htm本項目是我“從VHDL代碼到真實硬件”系列的第二部分,在該系列中,我們使用基于硬件的方法和可編程邏輯IC設計簡單的電子系統。這些系統為重要設計概念提供了極好的介紹,這些概念也可以應用于更復雜的項目。

有限狀態機項目概述

在這個項目中,我將介紹有限狀態機(FSM)的開發。具體來說,我將構建一個4位二進制計數器,帶有四個輸出LED和一個四位DIP開關模式輸入

邏輯將使用VHDL(一種硬件描述編程語言)編寫,并上傳到復雜可編程邏輯(CPLD)芯片。CPLD是一種可重復編程的現成邏輯門IC,類似于FPGA。

本項目將使用與我之前設計的8位算術邏輯單元(ALU)相同的硬件和軟件設置:

Altera Max II EPM240 CPLD開發板,

英特爾的Quartus Prime Lite版IDE。

如果您想復習可編程邏輯集成電路和Quartus Prime套件的基礎知識,您需要查看之前的項目。

什么是有限狀態機?

在深入設計之前,我們先快速回顧一下有限狀態機。有限狀態機是順序邏輯電路的抽象數學模型,在任何給定時刻,它只能在有限數量的狀態中運行。

FSM可以在每個時鐘周期在其狀態之間轉換一次。下一個狀態基于外部輸入和當前狀態(這意味著它使用了記憶邏輯)。

有限狀態機可用于檢測或生成序列,是電梯、交通燈、自動售貨機和電子鎖等系統的基礎。

二進制計數器

有限狀態機(FSM)的一種特殊實現是二進制計數器。這些電路的設計目標是迭代并顯示所需的二進制數序列,通常使用一系列相互連接的觸發器構建。二進制計數器的每個新狀態都必須由輸入脈沖觸發,該脈沖可以來自外部源或電路自己的時鐘信號。

有了這些背景知識,讓我們深入了解一下4位二進制計數器的代碼。

FSM二進制計數器的VHDL代碼

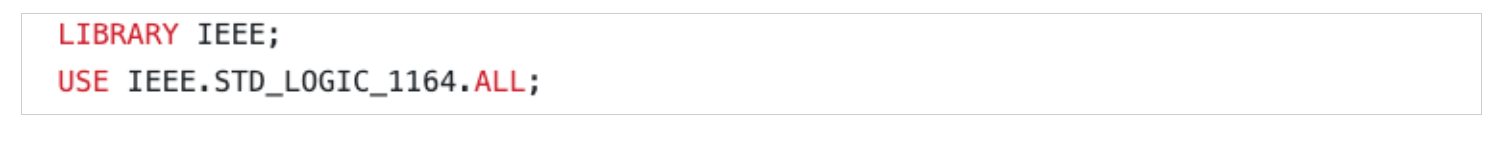

我們將在VHDL文件的頂部聲明幾個庫,開始為二進制計數器編寫代碼:

港口定義

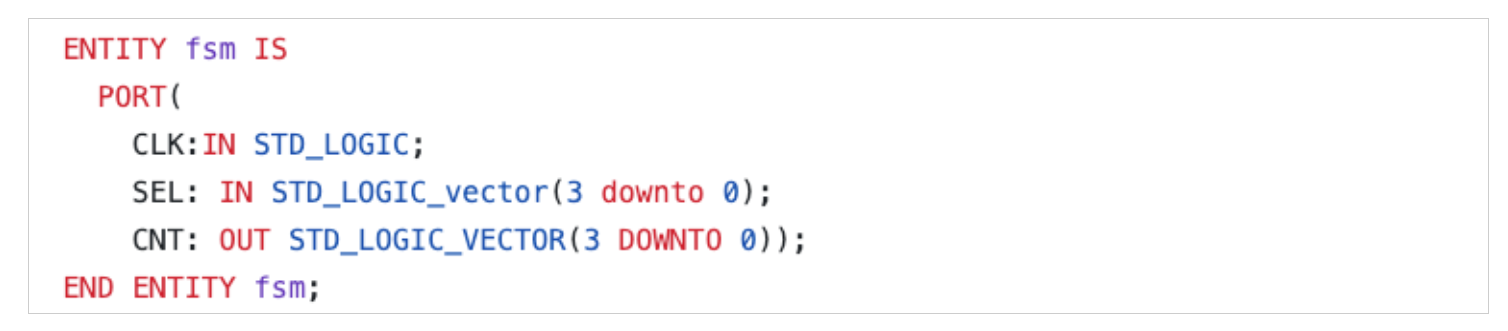

接下來,我們將為我們的電路創建一個名為fsm的實體,并定義其輸入和輸出端口:

在此代碼片段中,我們定義了:

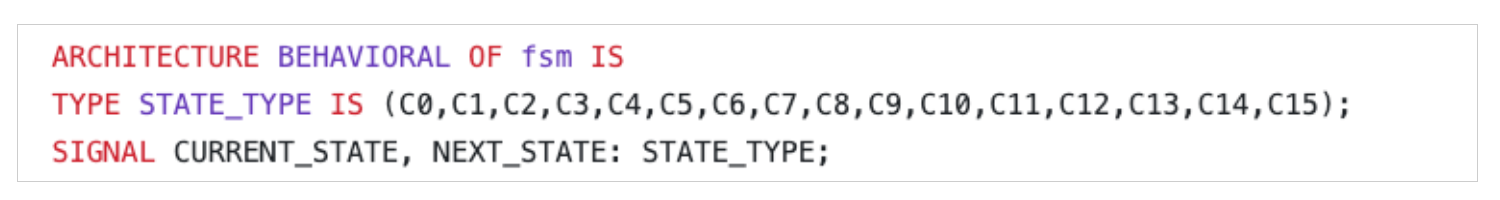

流程和數據類型定義

既然我們已經定義了FSM實體,我們就可以為我們的電路創建一個架構。這個架構將有三個過程:

狀態記憶。

下一個狀態邏輯。

輸出邏輯。

在創建這些進程之前,我們需要為我們的狀態定義一個新的數據類型,并為該數據類型定義兩個信號變量,用于記憶當前狀態和下一個狀態(將它們視為寄存器)。

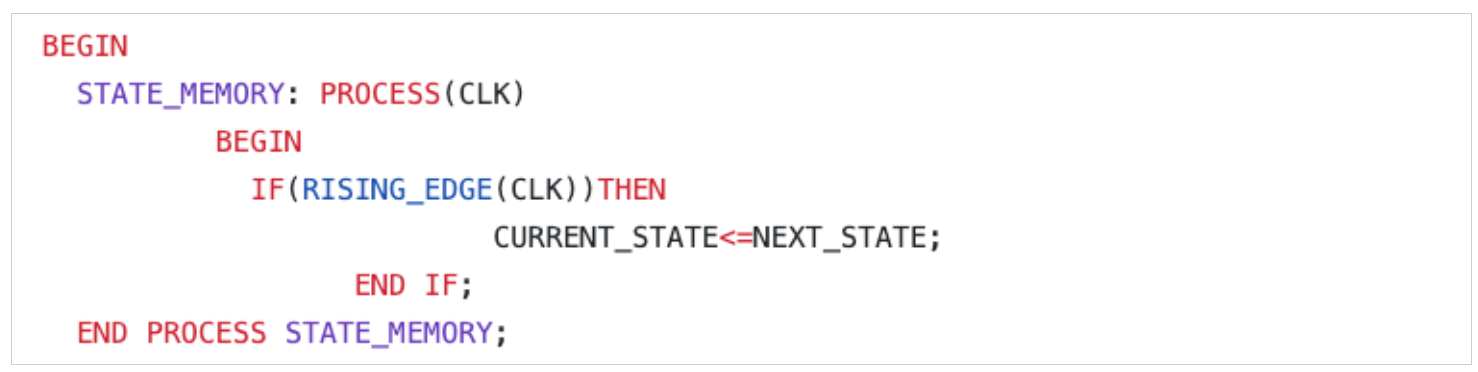

狀態記憶過程

現在我們可以創建第一個名為STATE_MEMORY的進程。使用IF語句,它會在CLK信號的每個上升沿將下一個狀態的值寫入當前狀態變量。

下一個狀態邏輯過程

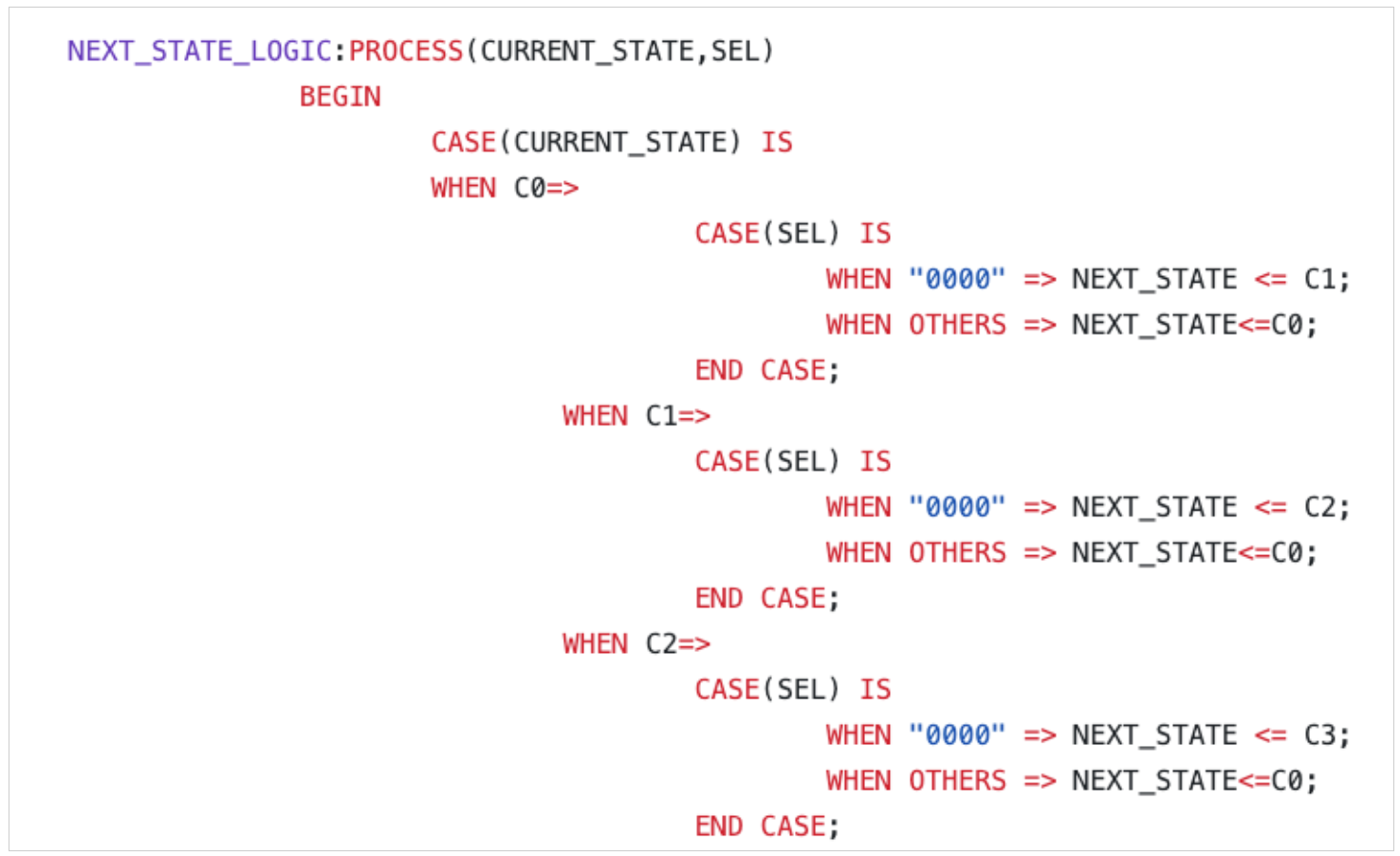

我們將使用SEL輸入端口和CURRENT_STATE信號創建一個名為NEXT_STATE_LOGIC的進程。在這個進程中,我們為當前狀態調用一個CASE-WHEN語句。我們在第一個CASE-WHEN語句的每個WHEN子句中嵌套其他CASE-WHEN語句以用于模式。

這樣,我們就有了一個架構,它首先檢查FSM的當前狀態,然后從SEL端口讀取值。當這個過程完成時,最后一個嵌套的WHEN子句將根據我們的代碼(對正在計數的序列)將正確的下一個狀態值寫入NEXT_STATE信號

下面的代碼塊顯示了一個簡單的向上計數器,當SEL端口值等于“0000”時,該計數器處于活動狀態。為了簡潔起見,這里只顯示了一些重復的case語句,但完整的代碼將在下面提供。

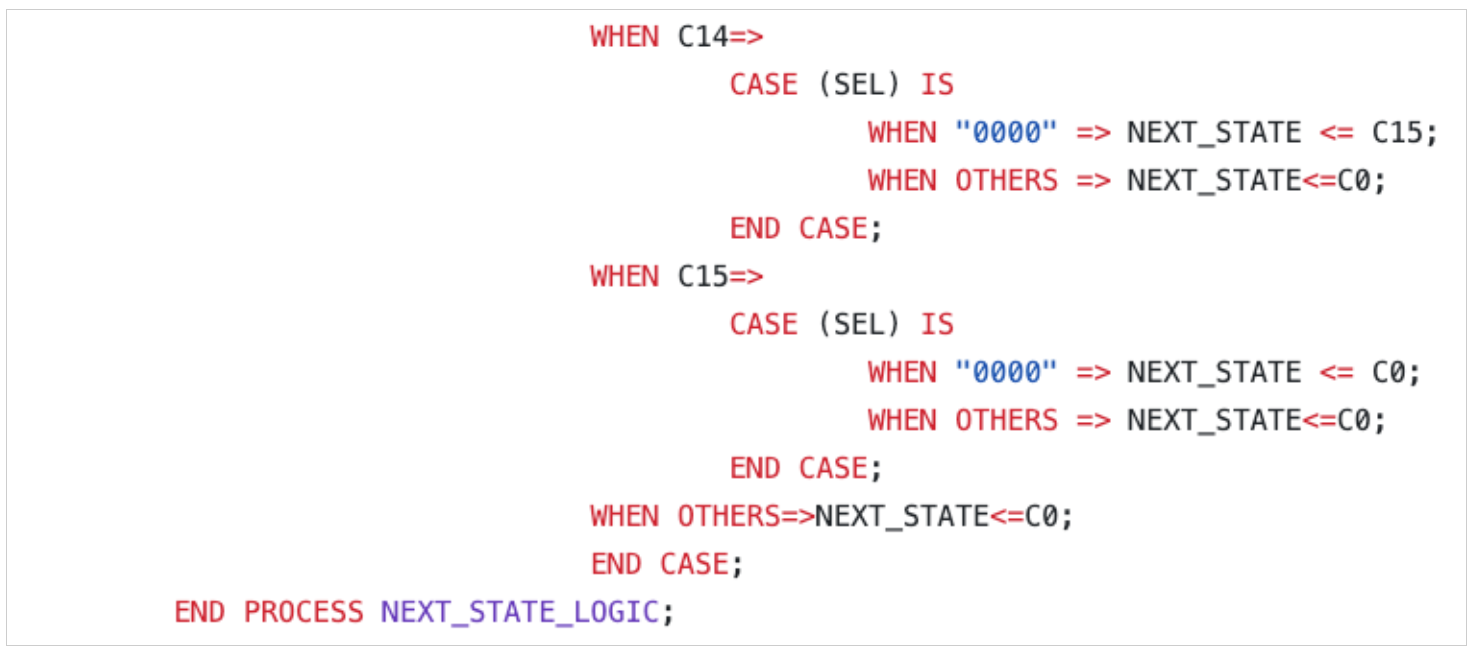

跳過案例,C3到C13是相似的,我們到達NEXT_STATE_LOGIC過程的末尾,我們有:

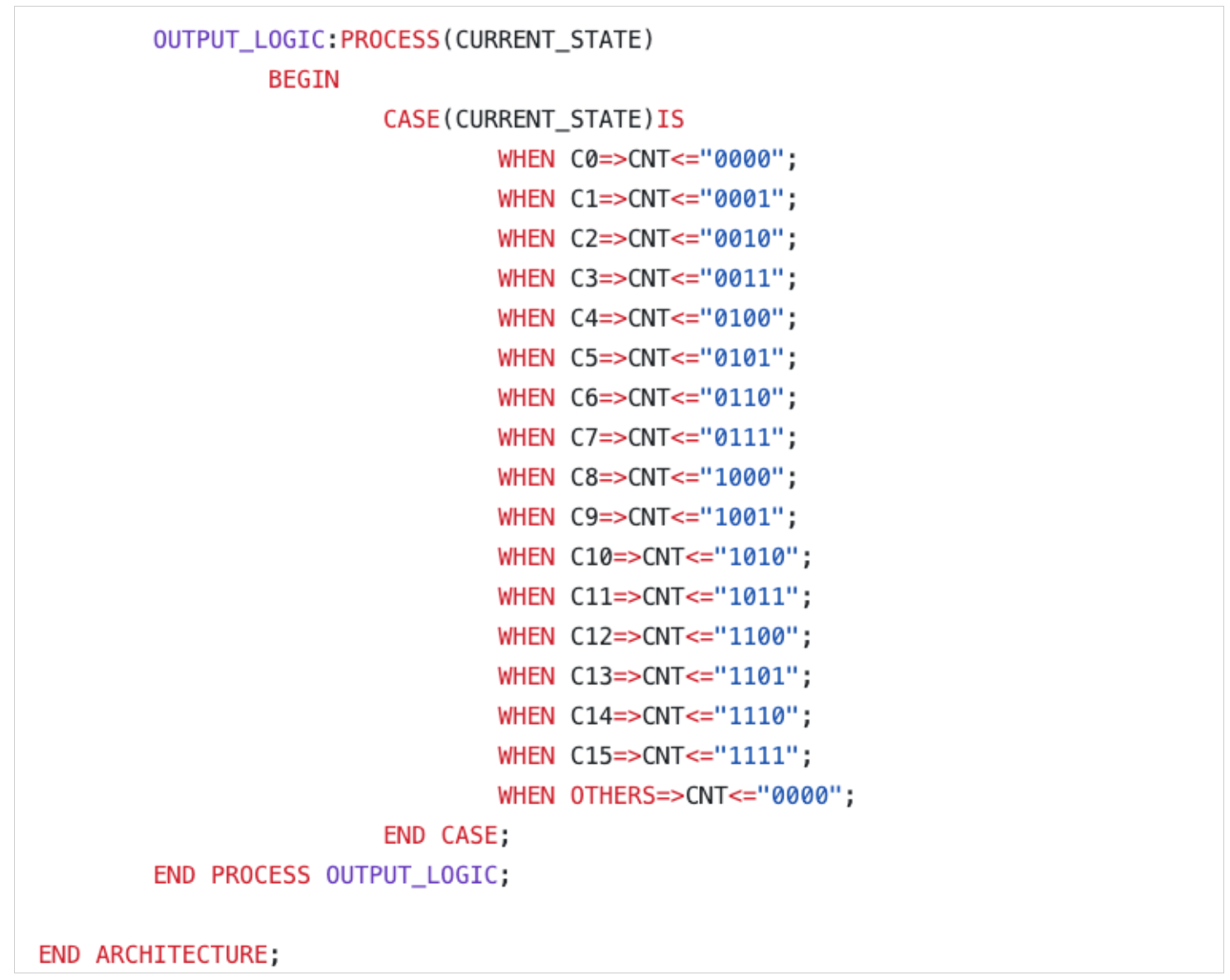

輸出邏輯流程

最后,為了在4位LED顯示屏上輸出當前狀態,我們需要編寫另一個名為OUTPUT_LOGIC的進程。它枚舉了我們之前定義的每種狀態類型,并配以相應的4位二進制數。

這同樣是通過使用CURRENT_STATE信號并調用另一個CASE-WHEN語句來完成的。CNT輸出表示當前狀態作為其4位二進制對應物:

編譯代碼

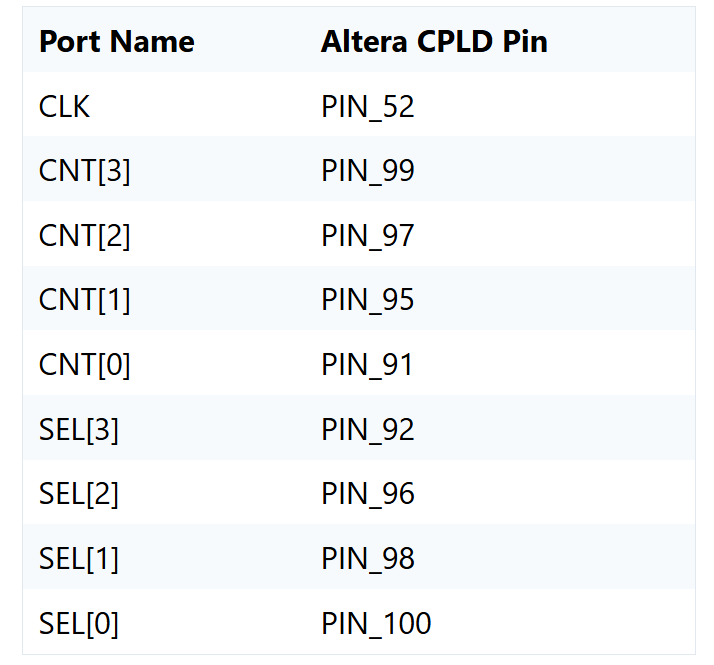

編寫代碼后,我們首先需要編譯它。然后,我們必須使用Quartus的Pin Planner工具,將我們在程序中定義的端口分配到Altera CPLD的物理引腳上,使用表1中顯示的映射。

表1. 端口到引腳映射

上傳到開發板

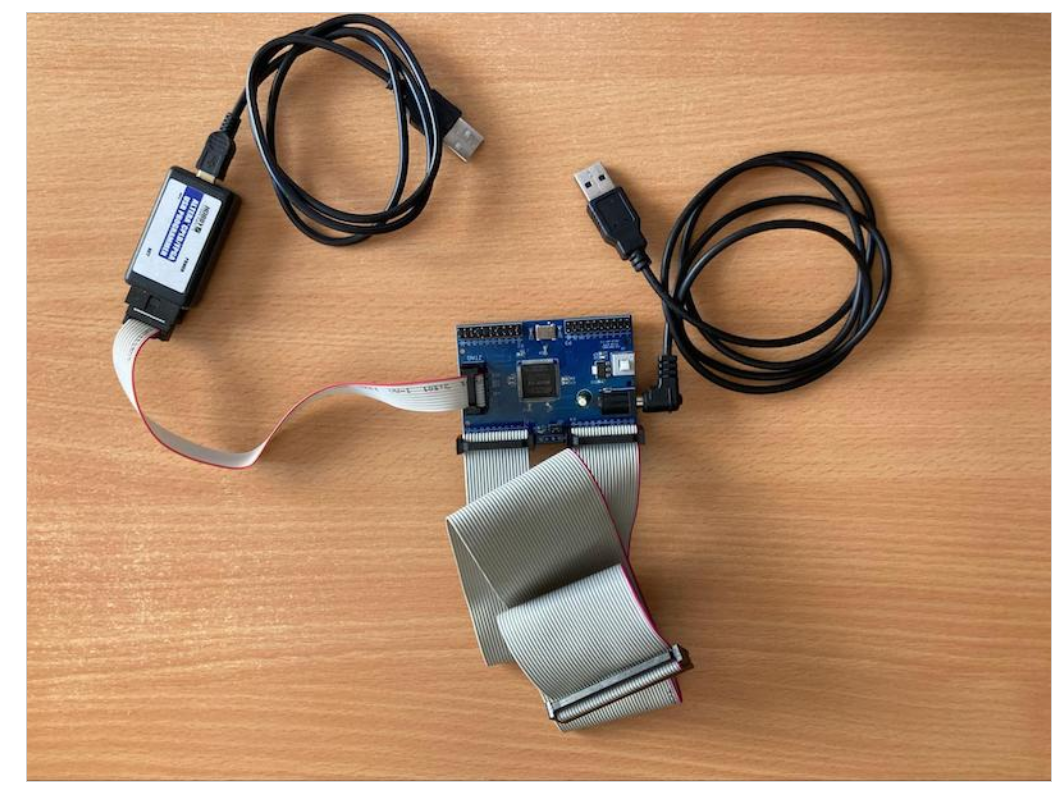

接下來,我們需要再次編譯代碼,然后才能最終將其上傳到開發板上。此過程是使用通過JTAG連接到Altera MAX II的USB Blaster進行的,如圖1所示。

Altera板和USB Blaster連接

圖1. Altera板和USB Blaster連接。圖片由Kristijan Nelkovski提供

添加外部觸發器

將代碼上傳到Altera板后,我們需要添加一個時鐘信號——某種類型的外部觸發器,使我們的計數器能夠遍歷其狀態。在這里,我要稍微作弊一下,使用運行默認Arduino Blink草圖的Raspberry Pi Pico,它充當我們電路的粗糙時鐘源。

您可以使用任何其他MCU開發板來實現此功能;只需確保向Altera MAX II發送3.3 V邏輯電平信號即可。Raspberry Pi Pico本身輸出3.3 V邏輯信號。

在我們的電路中,Blink草圖將提供0.5 Hz的時鐘信號(您可以在Arduino代碼的延遲部分更改頻率)。它不會讓LED閃爍一秒鐘,然后再熄滅一秒鐘,而是告訴我們的同步電路何時切換到其下一個狀態,如我們的VHDL代碼中所定義。

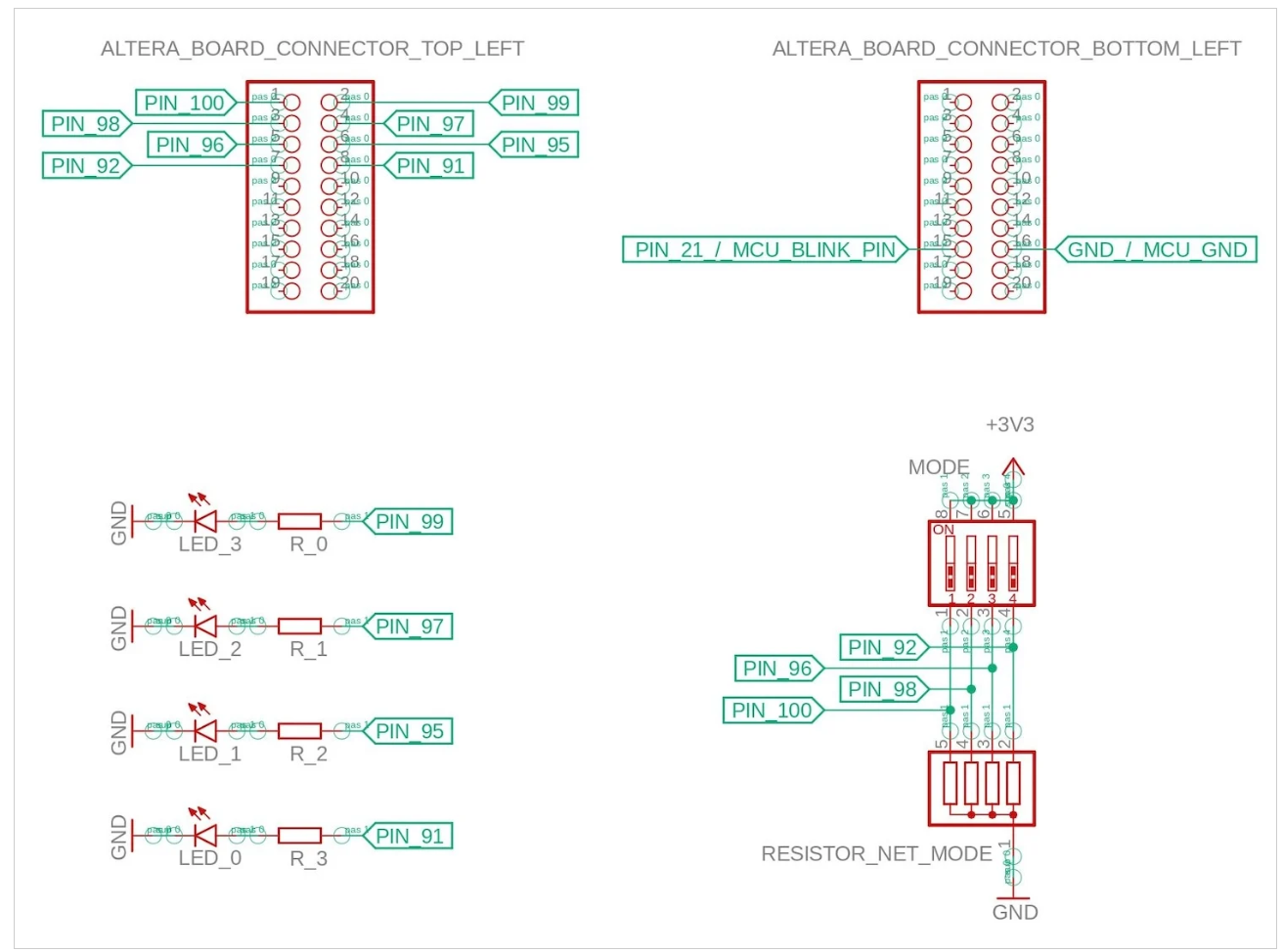

PCB電路圖

圖2中的示意圖顯示了項目的完整電路圖。在這里,每個LED都通過限流電阻連接到輸出引腳,連接到輸入引腳的DIP開關的每個觸點都通過電阻網絡下拉到地。然后,時鐘引腳連接到運行Blink的微控制器板上的假定LED引腳。

4位二進制計數器項目的電路原理圖

圖2:4位二進制計數器項目的電路示意圖。圖片由Kristijan Nelkovski提供

在將所有東西連接起來并為電路提供足夠的電源后,我們的FSM計數器應根據通過DIP開關選擇的計數模式,開始在其四個LED上迭代不同的二進制序列。

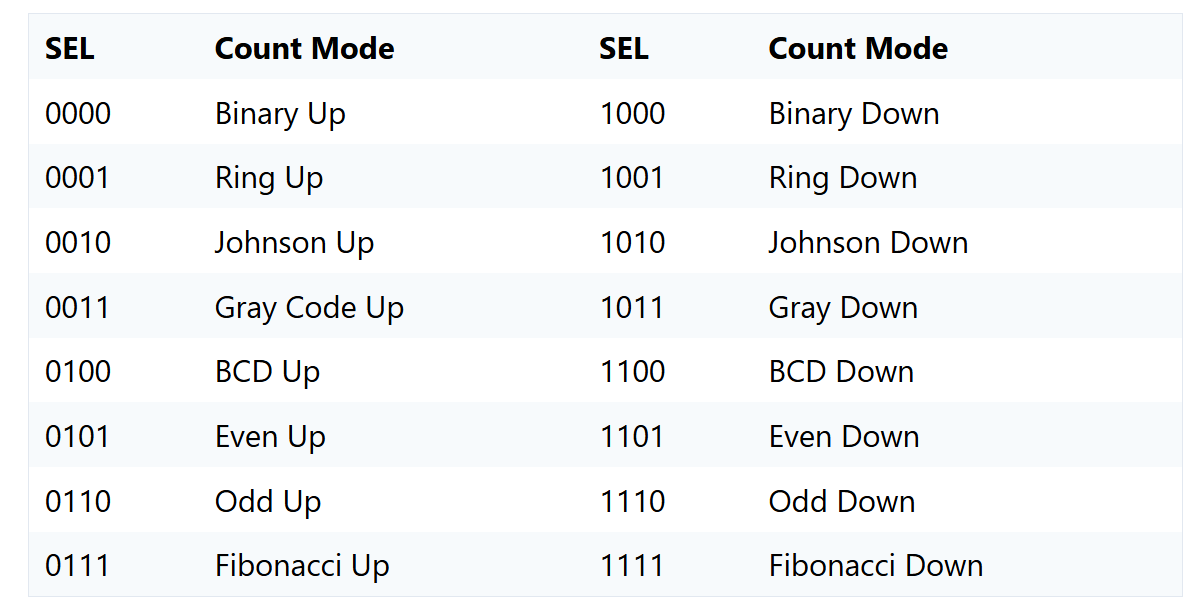

設計其他計數序列

對于SEL輸入的其他值,您可以創建任意4位數字序列。在本文末尾的完整代碼下載中,我包含了16種計數模式,可以使用表2中描述的4位SEL輸入進行選擇。

表2. 計數模式的SEL控制

注意:從技術上講,斐波那契數列應該重復出現1,但在這個簡單的項目中,這些序列中只有一個1。

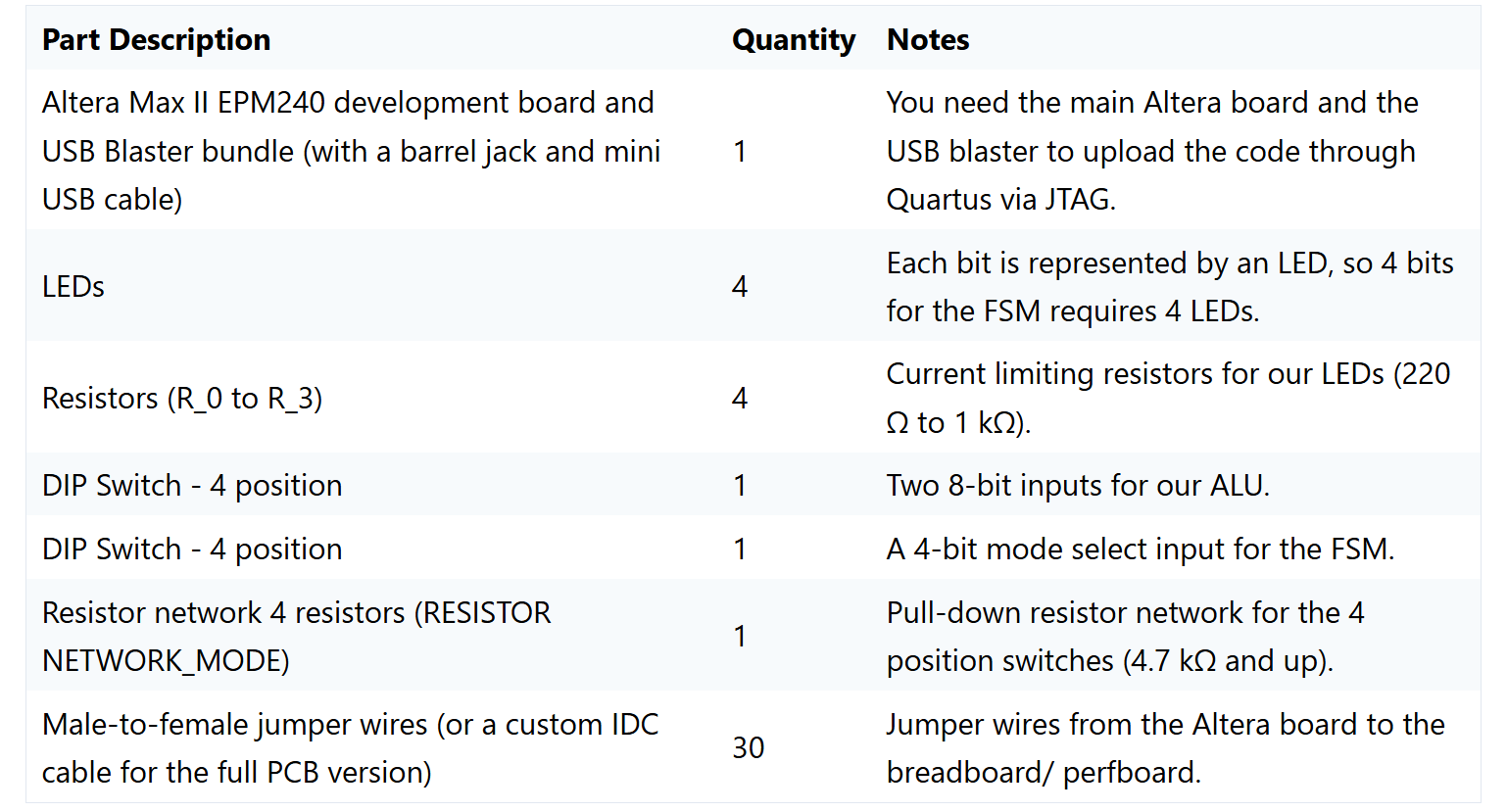

物料清單

表3包含項目物料清單(BOM)。

表3. 4位計數器物料清單。

輪到你了!

在這個項目中,我們使用VHDL硬件描述語言創建了一個有限狀態機電路,并在CPLD開發板上運行。本系列文章的目標是介紹可編程邏輯,并使用真實硬件而不是電路圖和計算機模擬來深入了解FPGA組件的實際使用。

如果你復制這個項目,你可以隨時修改代碼,切換計數模式,或者根據需要添加和刪除不同的序列。在下面的評論中分享你的想法和修改!

評論