初學者對有限狀態機(FSM)的設計的認識

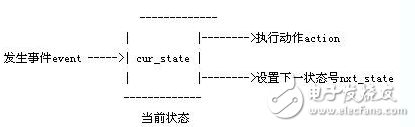

有限狀態機(FSM)是一種常見的電路,由時序電路和組合電路組成。設計有限狀態機的第一步是確定采用Moore狀態機還是采用Mealy狀態機。(Mealy型:狀態的轉變不僅和當前狀態有關,而且跟各輸入信號有關;Moore型:狀態的轉變只和當前狀態有關)。從實現電路功能來講,任何一種都可以實現同樣的功能。但他們的輸出時序不同,所以,在選擇使用那種狀態機時要根據具體情況而定,在此,把他們的主要區別介紹一下:

本文引用地址:http://www.czjhyjcfj.com/article/201710/365639.htm1. Moore狀態機:在時鐘脈沖的有限個門延時之后,輸出達到穩定。輸出會在一個完整的時鐘周期內保持穩定值,即使在該時鐘內輸入信號變化了,輸出信號也不會變化。輸入對輸出的影響要到下一個時鐘周期才能反映出來。把輸入和輸出分開,是Moore狀態機的重要特征。

2. Mealy狀態機:由于輸出直接受輸入影響,而輸入可以在時鐘周期的任一時刻變化,這就使得輸出狀態比Moore狀態機的輸出狀態提前一個周期到達。輸入信號的噪聲可能會出現在輸出信號上。

3. 對同一電路,使用Moore狀態機設計可能會比使用Mealy狀態機多出一些狀態。

根據他們的特征和要設計的電路的具體情況,就可以確定使用那種狀態機來實現功能。一旦確定狀態機,接下來就要構造狀態轉換圖。現在還沒有一個成熟的系統化狀態圖構造算法,所以,對于實現同一功能,可以構造出不同的狀態轉換圖。但一定要遵循結構化設計。在構造電路的狀態轉換圖時,使用互補原則可以幫助我們檢查設計過程中是否出現了錯誤。互補原則是指離開狀態圖節點的所有支路的條件必須是互補的。同一節點的任何2個或多個支路的條件不能同時為真。同時為真是我們設計不允許的。

在檢查無冗余狀態和錯誤條件后,就可以開始用verilog HDL來設計電路了。

評論