PCB設計:談談電源完整性仿真的必要性

隨著超大規模集成電路工藝的發展,芯片工作電壓越來越低,而工作速度越來越快,功耗越來越大,單板的密度也越來越高,因此對電源供應系統在整個工作頻帶內的穩定性提出了更高的要求。電源完整性設計的水平直接影響著系統的性能,如整機可靠性,信噪比與誤碼率,及EMI/EMC等重要指標。板級電源通道阻抗過高和同步開關噪聲SSN過大會帶來嚴重的電源完整性問題,這些會給器件及系統工作穩定性帶來致命的影響。PI設計就是通過合理的平面電容、分立電容、平面分割應用確保板級電源通道阻抗滿足要求,確保板級電源質量符合器件及產品要求,確保信號質量及器件、產品穩定工作。

本文引用地址:http://www.czjhyjcfj.com/article/201807/384136.htm電源完整性PI與信號完整性SI的相互影響:從整個仿真領域來看,剛開始大家都把注意力放在信號完整性上,但是實際上電源完整性和信號完整性是相互影響相互制約的。電源、地平面在供電的同時也給信號線提供參考回路,直接決定回流路徑,從而影響信號的完整性;同樣信號完整性的不同處理方法也會給電源系統帶來不同的沖擊,進而影響電源的完整性設計。所以對電源完整性和信號的完整性地融會貫通是很有益處的。設計工程師在掌握了信號完整性設計方法之后,充實電源完整性設計知識顯得很有必要。

電源完整性研究的內容:電源完整性仿真的內容很多,但主要的幾個方面如下:

1:板級電源通道阻抗仿真分析,在充分利用平面電容的基礎上,通過仿真分析確定旁路電容的數量、種類、位置等,以確保板級電源通道阻抗滿足器件穩定工作要求。

2:板級直流壓降仿真分析,確保板級電源通道滿足器件的壓降限制要求。

3:板級諧振分析,避免板級諧振對電源質量及EMI的致命影響等。

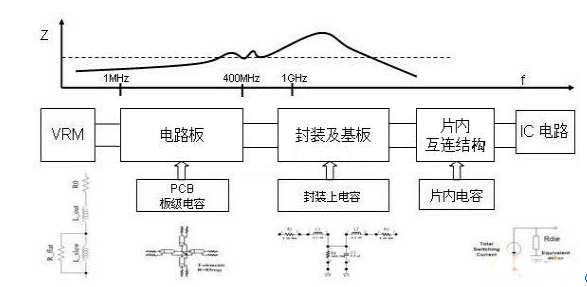

圖1 電源分配系統特性圖

電源分配系統(PDS):上圖是一張經典的電源分配系統特性 圖,相信大家都比較熟悉。從這個圖里面,我們可以將整個電源頻段分成幾部分。在低頻段,電源噪聲主要靠電源轉換芯片VRM來濾波。在幾MHZ到幾百MHZ的頻段,電源噪聲主要是由板級分立電容和PCB的電源地平面對來濾波。在高頻部分,電源噪聲主要是由PCB的電源地平面對和芯片內部的高頻電容來濾波。我們在做仿真的時候,對低頻和高頻部分的仿真精度都還不準確,真正有意義的頻段主要還是在幾MHZ到幾百MHZ這個頻段。

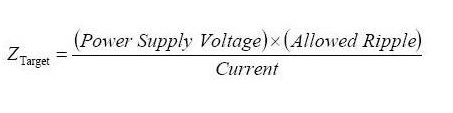

該聊聊大家都很熟悉的目標阻抗Ztarget了。筆者認為,這個目標阻抗是電源完整性仿真里的一個有用但不精確的標準。

其中:Ztarget目標阻抗

Power Supply Voltage是工作電壓

Allowed Ripple 是允許的工作電壓紋波系數

Current 是工作電流,目前這個值是用最大電流的1/2來替代。

大家都知道,電源測試的時候,主要是測試紋波,噪聲,但是業界目前還很難通過軟件進行時域的紋波噪聲仿真(一些大公司已經通過測試來建立芯片的噪聲模型, 然后用這個模型直接仿真,得到的結果就是電源噪聲,但目前還處于探索階段,沒有推廣使用),而是仿真電源分配系統的電源阻抗,他們的關系可以通過V=R/I來聯系。因此如果還是仿真阻抗曲線的話,測試與仿真不能形成閉環。

在衡量這個阻抗曲線是否能滿足要求的時候,使用了這個目標阻抗的標準,但是仔細想想,這個標準還是有很多問題的,比如:這里的電流多大合適?實際的單板功耗是一個動態功耗,是不端的變的。在單板的整個頻段范圍里,使用統一的目標阻抗值,肯定也是不合理的,應該是各個頻段,標準不一樣。

雖然有這些問題存在,但這個標準還是很有用的,可以通過這個標準衡量電源平面的好壞。就如目前的時序計算,大家基本上都是通過公式對時序進行計算,就是所 謂的靜態時序分析。雖然這個靜態時序分析對電源波動,ISI,SSN等問題考慮不周到,也就是說計算結果不準確,但用來衡量接口時序還是很有用的。因此筆 者認為,目標阻抗是一個有用而不準確的標準。

關于電容的資料很多,這里只做簡單介紹,下次將介紹在PI仿真里面很重要的平面板電容。

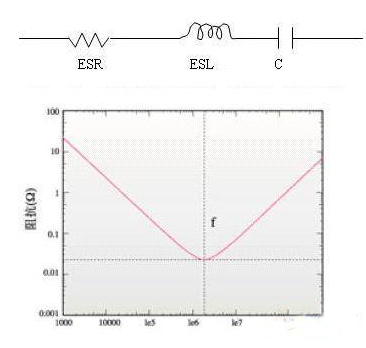

電容不僅僅是電容:在頻率很高時,電容不能再被當作一個理想的電容看,而應該充分考慮到它的寄生參數效應,通常電容的寄生參數為ESR,ESL。串聯的RLC電路在f處諧振。其曲線如下圖。圖中f為串聯諧振頻率(SRF),在f之前為容性,而在f之后,則為感性,相當一個電感,所以在選擇濾波電容時,必須使電容器工作在諧振頻率之前。

圖2 電容器在高頻時的曲線圖

在仿真的時候,由于目前VRM的模型基本上是不準確的,低頻的濾波靠DC/DC電源轉換芯片來完成,一般300K以下的低頻阻抗曲線是不準確地。頻率范圍的上限一般取信號的截止頻率fknee=0.35 /Trrise,其中Trise為信號上升時間。

但是也要明白一點,如果你只是做板級電源完整性仿真,最多考慮到1G就可以了,因為大于1G以后,要靠芯片內部的電容來濾波,在做板級仿真的時候,沒有芯 片內部的模型,所以高頻部分的仿真也是不準確的。當然了,如果您有芯片內部的信息,也可以用SIWAVE等軟件做DIE-PACKAGE-BOARD的協 同仿真,高頻部分也就準確了。

因此很多情況下,低頻仿真不出電源負反饋、高頻仿真不出芯片內電容, 我們不要把仿真的結果當做絕對值,可以把它當作是相對值,通過去耦電容的選擇和放置、電源和地平面的分割等方法來優化阻抗。祝愿各位在做仿真的時候能靈活運用。

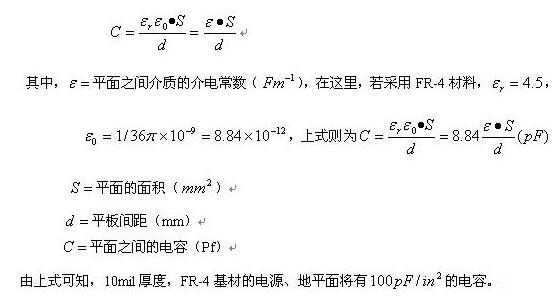

電源地平面可被當作一個平板電容器來對待,尤其在中低頻時,其ESR、ESL都很小。在這種情況下,電源、地平面作為一個去耦電容,對RF能量的抑制具有電容器無可比擬的優越性,通常電容器在500MHz以上,由于分布參數的影響,已經失去作用,而電源、地平面帽100MHz以上直到GHz的范圍內具有良好的去耦濾波特性。

電源、地平面的電容粗略計算為:

評論