3D IC設計打了死結?電源完整性分析僵局怎么破

數十年來,半導體行業在超級集成的道路上暢通無阻,一方面可以提高功能和性能,另一方面可以降低系統成本。不過,標準的做法是將越來越多的功能塞進單個裸片上,當您想要集成某些采用不同制程的功能時,這條路就走不通了。這就是為什么3D IC- 將3D模塊和內插器集成在一起變得越來越流行的原因。當前,一個流行的應用案例是將高帶寬存儲器與處理器并排結合在一起,在DRAM堆棧和主存儲器之間直接通過低阻抗/高度并行連接實現更高帶寬的通信。

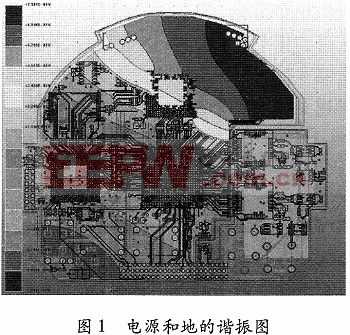

本文引用地址:http://www.czjhyjcfj.com/article/201709/364569.htm當然,每個設計創新都會帶來新的設計問題。其中之一就是如何管理這些系統一直到封裝和電路板級中的電源完整性。通常情況下,我們將電源完整性分析和配電網絡(PDN)設計視為能夠逐芯管理的功能,但是別忘了,我們之所以能夠這么認為,得益于封裝之間的高阻抗,以及芯片的高工作頻率最大程度減少了芯片間通信對片上功率噪聲的影響。但是,現在不僅存在一系列阻抗,諧振頻率也比較寬,包括低頻范圍的電路板級的MHz、中頻范圍的內插器層/TSV層的100 MHz和高頻級別的芯片級的GHz,這種特性意味著對電源完整性存在較大的潛在影響。即使我們可以忽略板級頻率的影響,這些中頻范圍內的頻率也絕對無法抹煞。

因此,在進行電源完整性分析時,不能再一廂情愿地認為每個芯片互相獨立互不相干了。至少要在整個3DIC的封裝內分析電源完整性。最近主辦的一個網絡研討會特別談論了這種類型的電源完整性分析。這種分析有兩個主要組成部分 - 一個是為整個3DIC設備構建一個精確的電源模型,可以在詳細的瞬態和AC Spice分析中使用,另一個是確保模型有效地反映了非常寬的響應范圍,包括從板級/封裝級的MHz到芯片級的GHz。

構建一個精確的電源模型需要考慮以下幾個層面。芯片/裸片的分析已經很成熟了,可以通過RedHawk或Totem(用于模擬設計)來實現。RedHawk還被推薦用于內插器提取,可以把內插器看做是制造技術文件支持的另一種半導體器件,RedHawk可以很好地完成這項任務。建議采用SIwave / HFSS處理TSV的提取。最后,這些可以組合成一個系統芯片功率模型(CPM),可以在芯片模型分析儀(CMA)中進行詳細的瞬態和AC分析。

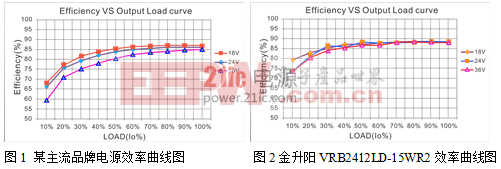

在分析的第二階段,重要的是確保CPM模型能夠反映整個系統所固有的廣泛響應范圍。在這個階段的芯片級分析中,可以查看幾十納秒的活動(上面的藍色部分)。但是,在更大的時間間隔上,不連續的事件可能會導致較大的功率轉換,比如3DIC封裝中另一個芯片從工作模式切換到空閑模式,或者板上另一個器件的活動(上面的紅色部分)。

在微秒范圍內進行納秒級別的精確分析是不切實際的。相反,CMA提供了基于芯片級高頻響應和低頻輸入構建代表性功率噪聲頻譜的工具,其中,低頻輸入可以通過各種反映內插器/ TSV和封裝/板對這些不連續性的響應的各種方法生成。然后,可以將這些頻譜合并,以生成更加準確地反映全部響應范圍的新CPM。

建模這些較長周期時間事件的方法包括分析長時間包絡,或者從PowerArtist配置文件中導出,或通過手動指定的配置文件(可用于反映板上傳感器的切換)導出,或通過基于針對該3DIC或者電路板的PDN生成對阻抗敏感的隨機噪聲。

由于這些3DIC器件具有從芯片到板級的大范圍諧振頻率,全面充分優化系統級PDN已經變得更加重要。顯然,現在需要更廣泛的分析。

評論