LEON3處理器動態圖像邊緣檢測的SoC設計

摘要:針對LEON3開源軟核處理器具有高性能,高可靠性等特征,構建了一個基于LEON3的動態圖像邊緣檢測SoC。文中采用局部熵邊緣檢測算法,將圖像采集,邊緣檢測和圖像顯示三個部分封裝設計為IP核,通過APB總線嵌入到LEON3的經典SoC架構中。與利用微控制器或DSP實現的動態圖像邊緣檢測系統相比.基于LEON3的動態圖像邊緣檢測SoC能夠充分發揮硬件設計的高速性和靈活性,并且系統具有很好的可移植性與可配置性,占用資源少,速度快,具有良好的應用前景。

引言

本文采用局部熵邊緣檢測算法,將圖像采集,邊緣檢測和圖像顯示三個部分封裝設計為IP(Intellectual Property)核,通過AMBA APB總線嵌入到LEON3的經典SoC架構中。實現了多路數據并行處理和DSP模塊加速處理,配合CPU軟核的協調參數配置功能,可以充分發揮硬件設計的高速性和靈活性。此外,由于動態圖像邊緣檢測是圖像處理應用中必不可少的一部分,因此文中設計的動態圖像邊緣檢測SoC可以方便的移植到其他圖像處理應用中,具有廣泛的應用前景。

1 SoC和LEON3開源軟核處理器

SoC是系統級芯片的簡稱,系統不僅包含了處理器內核、存儲器等硬件系統,同時還含有相應的嵌入式軟件,是一個真正的軟、硬件均具備的完整體系。利用SoC設計方法,可以將一個復雜的系統集成到單一芯片中,并具有低功耗,低成本及高速性的特點。與利用ASIC實現的

SoC相比,利用FPGA實現的SoC具有可配置性的特點,因此具有更好的可擴展性和可移植性。

LEON3開源軟核處理器是Gaisler Research公司提出的一款32位、符合SPARC V8結構的開源軟核處理器。它具有高性能,低復雜性和低功耗的優點。另外,所有屬于GRLIB的IP核及LEON3處理器的源代碼在GNU GPL(GNU General Public License,GNU通用公共許可證)授權協議下,可以免費地應用于研究和教學目的,因此,LEON3開源軟核處理器特別適合于SoC的開發設計。

2 SoC系統架構設計

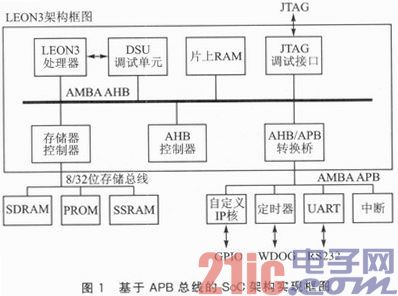

通過分析系統的功能與要求,結合LEON3自身架構的特點,設計基于APB總線的動態圖像邊緣檢測Soc系統架構如圖1所示。自定義IP核為本設計的重點。在LEON3的SoC架構中,APB外圍低速總線為一些低速模塊提供了接口。若想要在APB總線實現動態圖像的實時采集、處理和顯示,就要想辦法使采集到的數據不參與到總線傳輸中去。

在本設計中,通過采用片上存儲資源做FIFO的辦法,使得攝像頭采集到的數據得以緩存,最終在顯示器上顯示。在數據輸出顯示之前,可以選擇是否經過圖像邊緣檢測算法模塊處理。若經過模塊,則顯示圖像經過邊緣檢測后的結果;若不經過,則顯示原始圖像。

通過這種方法,避免大量圖像數據參與AHB與APB總線之間的數據傳輸,以減少不必要的中間過程,提高數據的實時性。這樣就避免了APB總線低速、低帶寬與動態圖像邊緣檢測系統高速、高帶寬的矛盾。使得整個圖像的數據流都在白定義IP核內部得到處理,這樣既滿足了APB總線的約束也實現了系統的功能需求。

3 動態圖像邊緣檢測SoC的實現

本設計提出了一種集圖像采集、存儲、處理和顯示于一個IP核的設計方法,也是動態圖像邊緣檢測SoC設計的核心部分。

3.1 局部熵算法的硬件實現

局部熵邊緣檢測算法的基本思想是:選擇待處理像素點的8鄰域,即以待處理像素點為中心的3×3窗口;再由局部熵的定義式(公式1)計算出圖像3×3窗口的局部熵;

然后通過與給定的閾值進行比較,得到二值化圖像,即可得出圖像的邊緣。硬件實現的處理過程為流水線方式,處理的對象為3×3大小的圖像窗口。具體步驟如下:

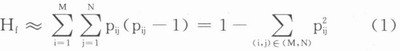

①3×3窗口的產生。3×3窗口主要通過片上緩存和延時單元實現。圖2是以經過3個時鐘為例說明了同步產生3×3窗口中一行數據的過程。

②熵值的計算。將步驟1中得到的3×3窗口的9個并行數據途經兩路進行處理。對于3×3窗口,式(1)化簡為式(2):

3×3窗口的9路并行數據,一邊送去做并行相加求和,再求平方,作為除法運算的分母;同時把9個數據分別求平方,再求合,作為除法運算的分子。在做除法運算前,為確保其計算精度,要先將分子與分母轉換成IEEE-745浮點數后再進行浮點除法運算。最后還要把除法運算的結算轉換成整數,考慮到除法運算的結果可能小于1,于是在轉換整數前放大1000倍,即保留3位有小數有效位,最后將轉換后的整數輸出,至此實現了局部熵值的計算過程。局部熵值計算的硬件處理流程如圖3所示:

③閾值比較及二值化處理。②中已經得到了放大1000倍后的熵值,在這里只需通過一個比較電路,當熵值大于閾值時,輸出0;當熵值小于閾值時,輸出1。這樣就得到一幅二值化后的邊緣圖像。至此,完成了整個局部熵邊緣檢測算法的硬件實現。

3.2 自定義IP接口設計

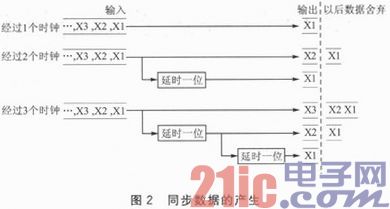

自定義IP核包含以下幾個主要部分:圖像采集(D5M攝像頭接口);圖像制式轉換;圖像存儲;圖像顯示(LTM顯示接口);圖像邊緣檢測模塊;自定義寄存器。

圖4給出了基于APB外圍低速總線所設計的圖像邊緣檢測IP核的外部接口信號圖。由圖中可知,此IP核的接口信號可分為:

①系統時鐘與復位信號:是整個LEON3架構所共用的時鐘信號和復位信號,而iCLK_50是由外部直接引入的頻率為50MHz的時鐘,未經過PLL處理。

②IP核控制信號:主要實現IP核的觸發功能和結束功能。

③APB總線的輸入信號和輸出信號:此信號主要用于APB總線控制、IP核選擇、IP核使能等,其中包括對IP核內部寄存器的設置都是通過APB總線信號來完成的。

④D5M攝像頭輸入信號和輸出信號:此信號主要完成對D5M攝像頭的配置以及數據采集。

⑤LTM顯示器輸入信號和輸出信號:此信號用于對LTM顯示器的配置。由于基于APB總線的IP核集成D5M攝像頭、LTM顯示器和邊緣檢測算法于一體,所以外部接口信號相對較多。但就APB總線本身而言,其信號并不多,這也是基于APB總線的設計方法相對簡單的原因。

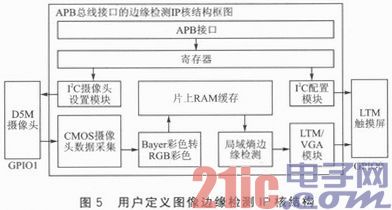

3.3 自定義IP核的結構設計

有關“基于APB外圍低速總線圖像檢測IP核的實現基本思想部分”略——編者注。

基于APB總線的IP核框架結構如圖5所示。

4 實驗結果

4.1 動態圖像邊緣檢測算法硬件實現仿真與分析

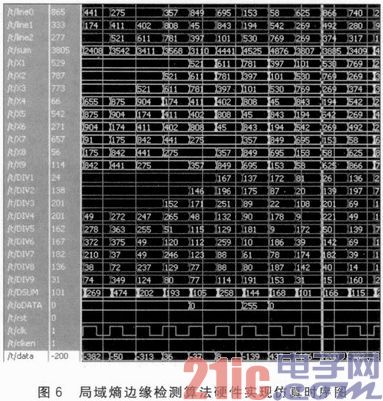

文中首先利用Matlab驗證局域熵邊緣檢測算法設計的正確性,然后采用Verilog HDL硬件描述語言編寫圖像邊緣檢測算法,在算法實現過程中,為提高算法的性能,采用了Quartus II中自帶的DSP加速宏模塊。同時,為驗證仿真算法的正確性,編寫Testbench系統測試文件,對其進行仿真驗證,圖6為局域熵邊緣檢測算法的硬件仿真時序圖。

從圖6中,可以看到3×3窗口產生的過程,L1~L3為采用片上緩存的方法實現的三行數據的同步。X1~X9對應3×3窗口中的9個像素點。圖中最終的數據輸出是有一定時延的,這是由于算法中存在大量的乘加運算和浮點數運算造成的。

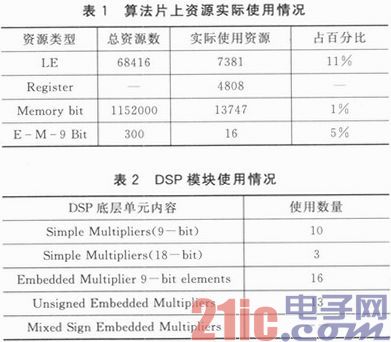

在實現算法的同時,考慮到所選芯片提供了可用于加速算術運算的DSP模塊,于是為了加速算法的處理速度,在算法實現過程中,加入了大量的DSP加速處理模塊,如乘加器,浮點除法器等。表1給出了用硬件語言實現上述算法所使用的芯片資源情況。表2給出了該算法對DSP加速模塊的使用情況。

4.2 動態圖像邊緣檢測SoC系統性能測試

測試采用的硬件開發平臺為FPGA CycloneIIEP2C70F896C6N,Quartus II版本為10.0(32位),LEON3開發包版本為grlib-gp1-1.0.22-b4095.zip。D5M攝像頭工作在25MHz頻率,所采集的圖像分辨率為400×240,R、G、B每種色彩以10-bit二進制數據表示,D5M攝像頭每秒采集22~25幀圖像。LTM顯示屏的顯示分辨率為400×240,工作在33MHz頻率。

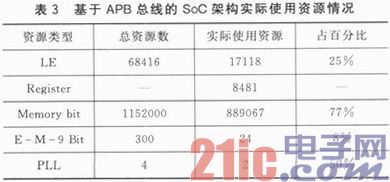

表3為測試得到的片上資源使用情況。圖7為文中設計的動態圖像邊緣檢測SoC系統工作實物圖。從其結果可以分析得到,文中設計的動態圖像邊緣檢測SoC占據的片上資源在可以接受的范圍內。

且由實際測試可知,在外界環境適中的條件下,系統可以得到很好的圖像邊緣檢測效果。但由于圖像的分辨率較大,而邊緣檢測算法中所采用的窗口為3×3,相對于圖像來說較小,所以圖像上的一些小的陰影區域也會被檢測出來,形成陰影區域干擾,影響圖像的邊緣檢測效果。但總體來說,實現了動態圖像邊緣提取的最終目的。

結語

本文介紹了基于LEON3開源軟核處理器的動態圖像邊緣檢測SoC設計。

實驗結果表明該SoC系統工作正常,可以實現每秒22~25幀,最佳分辨率為400×240和640×480的動態圖像邊緣檢測功能,平均數據延時在70~80個系統時鐘。系統具有很好的可移植性與可配置性,占用資源少,速度快,具有廣泛的應用前景。

評論