基于ADC和FPGA脈沖信號測量設計

0引言

本文引用地址:http://www.czjhyjcfj.com/article/195622.htm測頻和測脈寬現在有多種方法。通常基于MCU的信號參數測量,由于其MCU工作頻率很低,所以能夠達到的精度也比較低,而基于AD10200和FPGA的時域測量精度往往可達10 ns,頻率測量精度在100 kHz以內。適應信號的脈寬范圍在100 ns~1 ms之間;重復周期在0.05~100ms:頻率在0.1 Hz~50 MHz。

AD10200是高速采樣芯片,其中內嵌變壓器,因此采樣電路外部不再需要變壓器,使得電路設計更為簡單;最低采樣速率為105 MSPS,具有3.3 V或者5 V CMOS兼容輸出電平,雙通道12位采樣,補碼形式輸出,每個通道功耗為0.850W。通常可應用于雷達中頻信號接收機、相位組接收機、通信接收機、GPS抗干擾接收機等。

StratixⅡ是Altera公司的中高端主流產品,該產品采用1.2 V、90 nm、9層信號走線,全銅SRAM工藝制造。StratixⅡ內嵌RAM塊、DSP塊、鎖相環(PLL)和外部存儲器接口,同時,StratixⅡ也增加了全新的邏輯結構一自適應邏輯模塊(ALM),因而增加了動態相位對準(DPA)電路和對新的外部存儲器接口的支持。AD芯片可以穩定工作在100 MHz,FPGA速度可高達幾百MHz,故可保證系統的測量精度。

1測量原理

1.1時域測量原理

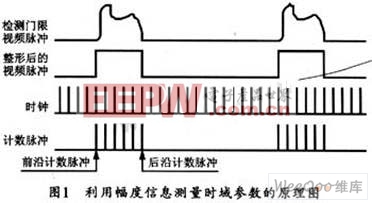

時域測量包括脈寬(PW)測量和脈沖重復周期(Pri)測量,時域測量在FPGA中可利用數字化技術實現。AD的兩路輸入為兩路正交中頻信號。經過Cordic算法,即幅相解算之后獲得幅度和相位信息,其中利用幅度信息測得時域參數,其原理圖如圖1所示。

當脈沖信號進入FPGA后,將首先進行門限判定,以將不規則的脈沖信號進行整形并變為規則的脈沖信號。整形后,在脈沖信號上升沿啟動脈寬計數器和重復周期計數器,而在該脈沖信號的下降沿鎖存脈寬計數器并且在下個脈沖信號上升沿鎖存重復周期計數器;由此即可得到脈寬和重復周期的量化值N和M,然后再通過工作時鐘的計算,就可得出脈寬和重復周期。

評論