基于C++TCL PLI聯合仿真下的芯片驗證方法研究

0 引 言

當今社會,芯片技術與人們的生活密切相關,在各種電子產品中都有芯片的身影,而且,它們往往是電子產品關鍵的核心技術。制造芯片的流程非常復雜而且資源投入巨大,保證芯片的設計質量非常重要。驗證工作是芯片制造過程中及其關鍵的一個環節,無缺陷的芯片不是設計出來的,而是驗證出來的,驗證過程是否準確與完備,在一定程度上決定了一個芯片的命運。

目前在百萬門級以上的ASIC,IP,SoC設計時代,驗證約消耗整個設計工作的70%,需要專職的驗證團隊,而且驗證團隊人數通常是設計團隊的1.5~2倍。隨著設計規模的擴大,芯片驗證的重要性達到了一個新的高度,但對驗證方法也提出了更多的要求,怎樣搭建高效穩定的驗證模型成為目前研究的熱點。本文重點介紹如何搭建一種分層次的驗證模型,以及如何使用這套驗證模型進行仿真。

1 驗證架構

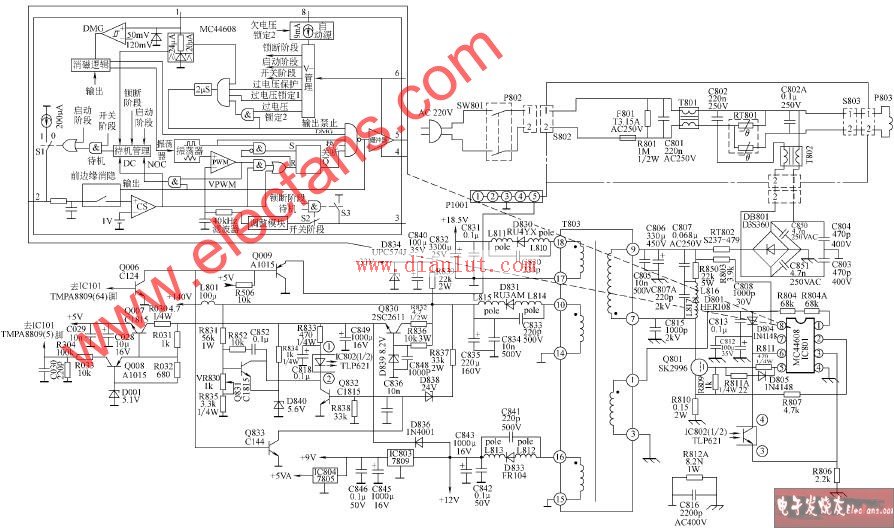

驗證架構通常稱為testbench,如圖1所示,可以把驗證架構分為激勵源、發送器、接收器、參考模型和記分牌五個部分。激勵源屬于腳本層,發送器和接收器屬于時序層,參考模型和記分牌屬于軟件層。

激勵源 仿真的數據在激勵源中生成,它是一個TCL腳本語言解釋器,激勵代碼采用TCL解釋性腳本語言編寫,激勵生成之后會放到發送端共享緩存區中,這個過程在設計代碼開始仿真之前。

發送器 當仿真開始后發送器會根據設計條件把數據從發送端共享緩存區中取出來,傳遞到設計模塊和參考模型中,發送器由Verilog代碼編寫實現,需要設計自己的PLI函數用來作為與發送端共享緩存區傳遞數據的接口。

接收器 接收器用來采集設計模塊處理后的數據,并把數據放到接收端共享緩存區中,用于記分牌讀取數據,接收器由Verilog代碼編寫實現,需要設計自己的PLI函數用來作為和接收端共享緩存區傳遞數據的接口。

參考模型分析激勵源的數據并產生和設計模塊用來校驗結果,由于驗證人員和設計人員的理解思路不同,參考模型的功能和設計模塊的功能也不同,但隨著驗證過程的推進,兩者應該收斂于需求規格書,參考模型基于C++語言實現。記分牌記分牌從接收端共享緩存區取出數據和參考模型的分析結果并進行比較,把每次比較的結果記錄下來,以便驗證人員定位問題,記分牌基于C++語言實現。

評論