用于帶有PCIe的嵌入式系統的散/聚式DMA

新一代的互聯需求持續不斷地向軟硬件設計施加壓力。不斷提高的服務質量(QoS),數據信道隔離,數據平滑恢復和完整性等,都是值得考慮的一些指標要求。PCIe就是能夠滿足上述要求的一種互聯技術。

本文引用地址:http://www.czjhyjcfj.com/article/191787.htm在FPGA中實現一個PCIe接口時,為了確保系統效率,系統抖動,數據時鐘開銷以及必須滿足的端到端總帶寬需求,設計師必須考慮數據傳輸的方式。將一個散/聚DMA(SGDMA)與一個PCIe接口結合起來,通過從本地處理器上卸載一些數據傳輸負擔,以及均攤多通道間的硬件延遲,非常有助于軟硬件設計師滿足他們的設計需求。本文將討論采用基于FPGA的SGDMA與PCIe相結合的一些優點。

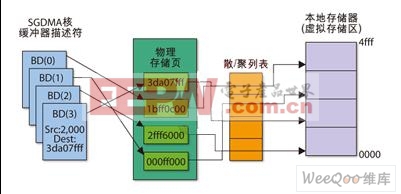

絕大部分的新型DMA控制器都支持散/聚功能,這里,硬件負責數據的轉移,駐留在不連續的物理存儲器中,不需要主處理器來處理模塊間的數據轉移。這是通過將DMA緩沖器描述符“鏈接”到一起來實現的,每個描述符中都含有使SGDMA自動執行數據轉移所需的所有信息。當處理支持虛擬存儲器的操作系統時,SGDMA得到最普遍的采用。

直接存儲器訪問實現方案

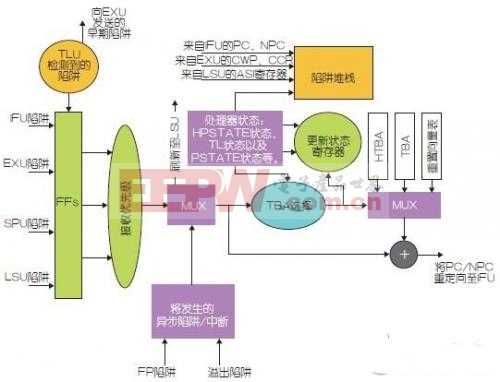

衡量DMA控制器的收益有以下幾種方法:通過定量分析究竟重新獲取了多少時鐘周期?相關設備驅動的復雜度減少了多少?或者由于“隱藏”數據分發的開銷使DMA引擎增加了多少系統總吞吐量?增強型DMA引擎支持的一些功能包括:

* 在線分組緩沖存儲

* 本地和前端總線的同時傳輸

* 延時處理

* 終端事物處理搶斷

* 為DMA控制器連接的每條總線提供獨立仲裁

當前端和本地總線處于超高負載條件下且傳輸數據前DMA控制器必須競用并獲取總線占有權時,可以采用在線數據緩沖器。

圖1:虛擬存儲器環境中的SGDMA控制器。

在FPGA中使用塊存儲始終是下面幾方面的折中,即由于總線占用究竟需要多少臨時緩沖器?FPGA中的功能是否需要存儲器?使用中間數據存儲所導致的附加延遲的代價如何?如果可能的話,在線分組緩沖器可以減少一些系統延遲,即用一條總線去讀取數據,而“存儲”總線不轉送數據。

評論