用于帶有PCIe的嵌入式系統的散/聚式DMA

1. PCIe用在所有的事務層分組(TLPs)方面的開銷相對固定;較多的數據包則需要較多的處理開銷

2. 較小的數據包通常需要的處理時間也少,于是就增加了由數據引擎和PCIe接口發起的并發中斷的次數

3. 為了維持適當的負載均衡,較小的數據包會增加本地處理器的負荷

4. 本地主處理器必須花費較多的時間來生成PCIe協議所用的數據轉移TLP

上面的幾點意味著本地主處理器將會損失更多的原本用于其他功能的時鐘周期。因此,較小的數據包有助于減小物理接口的處理延遲,但代價是增加了終端系統的負荷,這有可能降低總的系統性能。雖然PCIe TLP開銷處理延遲無法完全消除,但通過采用一個多通道散/聚DMA引擎,基于靈活的仲裁機制,將數據塊請求分成較小單元的可變大小的數據包,以及在DMA控制器自身中設計事務分割支持能力,可以攤薄每隔通道上與每個流等級(TC)相關的延遲。此外,設計一個較小的TLP事務IP核,通過生成/終接PCIe TLP,有助于提高軟件的效率。

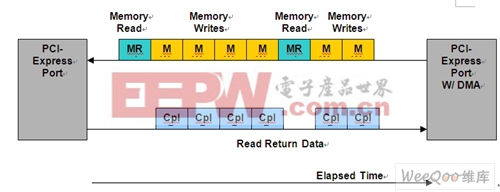

圖3:帶有DMA的PCIe讀/寫處理。

對于PCIe,存儲器讀取(MRd)不是優先的,是作為一個分割事務執行的,而存儲器寫(MWr)則是優先的。對于讀取,請求者先發送一個MRd TLP來請求completor算法發送大量的數據(通常最大的讀取請求為512字節),然后專門等待發送過來的數據。PCIe MWr TLP中包含將被寫入(通常最大為128字節)的滿載荷。因此,MLRd TLP在發送方向上,就像MWr TLP那樣,也需要一段帶寬。通過向MW通道分配更多的資源,在發送(Tx)方向上管道將保持在滿狀態,而接收(Rx)管道則用響應MRd請求的數據TLP來填滿,見圖2。

軟件執行時間方面獲得的好處

一個功能豐富的散/聚DMA控制器通過實現其他方案中需要復雜的算法和/或大量中斷的功能,還能夠減少軟件開發的工作量和CPU的執行時間:

* 所有最先進的處理器和操作系統,包括實時性能最好的操作系統(RTOS),都采用MMU和虛擬存儲器。乃至內核都采用虛擬地址。這意味著DMA不能線形地訪問系統存儲器中的緩沖器。當該緩沖器接近處理時,事實上它被散布到PAGE_SIZE模塊中的各個物理存儲器中。一個散/聚DMA通過允許每個緩沖器描述符被映射到存儲器的物理頁中,來幫助處理器和軟件驅動器。在本地緩沖器描述符中沒有散/聚列表,驅動器一次只能移動一頁的數據,然后才能重新啟動DMA進行下一頁的移動,這樣將很大程度上影響系統性能。

* 通常,一個系統由多個執行線程組成。這些線程可能都要轉移數據。如果一個DMA由多個通道,并為每個通道都分配一個線程,就能通過這些更多的并行處理來改善系統性能。

* 如果CPU工作在little-endian模式并轉移TCP/IP數據包到MAC,通常被迫利用軟件例程來與網絡order(big-endian)交換字節。一個能夠在硬件中以即時模式實現這種轉換的DMA,能夠降低軟件的復雜度并縮短系統設計時間。

* 為了提高效率,PCIe總線接口應該盡可能寬(64位),不過許多外設卻只具有窄帶寬(16或32位)。如果用DMA進行總線重新適配,則對PCIe接口的性能沒有影響,在構建高帶寬轉移到PCIe接口邏輯之前,DMA可以對較小的外設進行2重或4重訪問。

* 它提供了一個適配層,將基于分組的TLP數據流轉換成對線形存儲器的并行總線訪問。這對于復用已經帶有存儲器接口(地址總線,數據總線,控制線)的IP模塊的設計師來說將帶來巨大的收益。他們能夠非常容易地將IP模塊配置到DMA服務的總線上。

本文小結

利用像散/聚DMA控制器這類先進的載荷存儲數據引擎控制器,FPGA系統設計師能夠改進與基于PCIe的系統設計相關的軟硬件中普遍存在的吞吐率和延遲方面的缺陷。

評論