基于CPLD和ISA總線的數據采集系統設計

摘要:介紹一種基于復雜可編程邏輯器件(CPLD)的數據采集系統,并給出詳細的設計方案。計算機通過ISA總線實現與數據采集系統的指令和數據傳輸。通過VHDL編程實現CPLD對12位串行模數轉換器ADS7816的控制。最后,給出該系統設計的仿真波形和測試結果。

關鍵詞:CPLD;數據采集;ISA總線;VHDL

數據采集是工業測量和控制系統中的重要部分。它是測控現場的模擬信號源與上位機之間的接口,其任務是采集現場連續變化的被測信號。系統應將所采集的模擬數據信號盡可能真實、不失真地顯示給控制人員。

隨著計算機技術和EDA技術的發展,由于復雜可編程邏輯器件(CPLD)具有高集成度、小體積、低成本、低功耗以及高穩定性等諸多優點而廣泛使用到諸如傳統工業控制等各個領域。基于ISA的接口電路,其布線要求遠沒有PCI或USB接口板高。由于它能夠提供16位I/O操作,對I/O的直接讀寫可以完全不考慮復雜的驅動程序和應用程序,因而在ISA總線上開發接口電路目前仍是首先考慮的方法。因此,這里提出一種基于CPLD和ISA總線的數據采集系統設計。

1 系統硬件設計

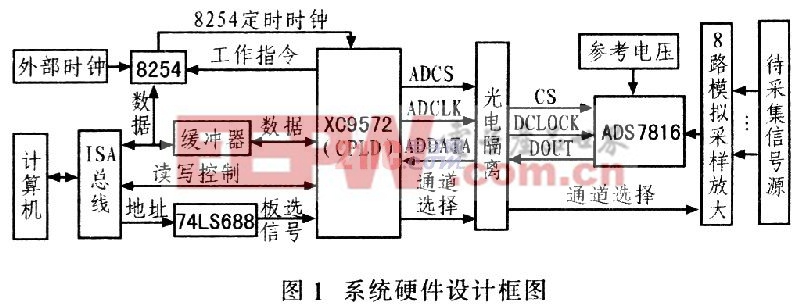

數據采集系統的硬件電路主要包括:CPLD邏輯控制電路、8254定時器電路、A/D轉換電路。該系統硬件設計框圖如圖1所示。

1.1 CPLD邏輯控制電路

該系統使用XC9572作為主控器件。XC9572是一款高性能可編程邏輯器件,內含4個36 v 18功能模塊,具有l 600個可用系統門。ISA總線上的地址、控制指令和數據被送進CPLD,經處理后送到相應電路中。由A/D轉換電路得到的數據也返回到CPLD進行處理,并經ISA總線送至計算機中。

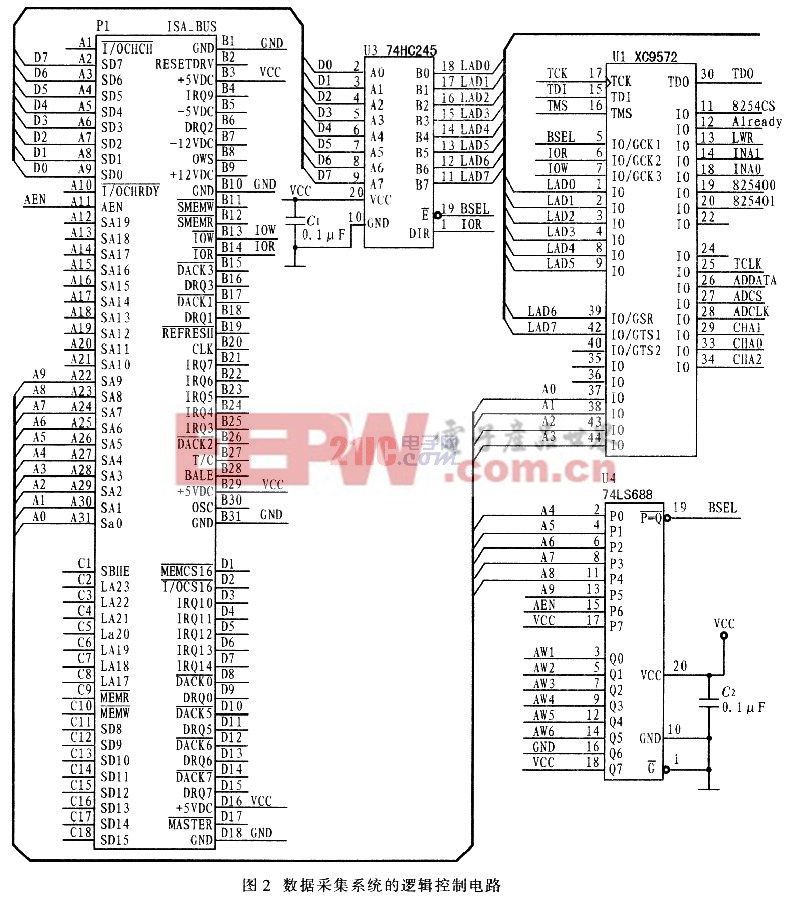

圖2為數據采集系統的邏輯控制電路,Ul是數據緩沖器74HC245,由lSA總線的讀/寫信號(IOR/IOW)和板卡選擇信號(BSEL)決定數據的流向。比較器74LS688和XFl組成板卡選擇信號發生電路。通過在XFl上的跳線可確定采集系統板的基地址。該系統基地址設置為280H。

ISA總線上的讀寫信號,經緩沖器的數據信號(LADO~LAD7),地址信號(A0~A3)均與XC29572相連,CPLD發送A/D轉換器的片選信號(ADCS)、A/D時鐘信號(ADCLK)以及通道選擇信號(CHA0~CHA2)。

評論