基于FPGA的DDS設(shè)計(jì)

摘要:利用現(xiàn)場可編程門陣列(FPGA)設(shè)計(jì)并實(shí)現(xiàn)直接數(shù)字頻率合成器(DDS)。結(jié)合DDS的結(jié)構(gòu)和原理,給出系統(tǒng)設(shè)計(jì)方法,并推導(dǎo)得到參考頻率與輸出頻率間的關(guān)系。DDS具有高穩(wěn)定度,高分辨率和高轉(zhuǎn)換速度,同時利用Ahera公司FPGA內(nèi)的Nios軟核設(shè)置和顯示輸出頻率,方便且集成度高。

關(guān)鍵詞:現(xiàn)場可編程門陣列;直接數(shù)字頻率合成器;Nios;VHDL

直接數(shù)字頻率合成DDS(Direct Digital Synthesis)是一種把一系列數(shù)字信號通過D/A轉(zhuǎn)換器轉(zhuǎn)換為模擬信號的合成技術(shù)。該技術(shù)的主要特點(diǎn):具有超高的捷變速度(0.1μs)、超細(xì)的分辨率(可達(dá)1μHz)和相位的連續(xù)性;輸出頻率的穩(wěn)定度及相位噪聲等指標(biāo)與系統(tǒng)時鐘相當(dāng);全數(shù)字化便于單片集成等。基于以上優(yōu)點(diǎn),DDS得到廣泛應(yīng)用,但由于其輸出帶寬小和雜散指標(biāo)不高,限制了其應(yīng)用范圍。

現(xiàn)有的DDS產(chǎn)品應(yīng)用于接收機(jī)本振、信號發(fā)生器、通信系統(tǒng)、雷達(dá)系統(tǒng)等,特別是跳頻通信系統(tǒng)。這里介紹基于FP-GA的DDS信號源,可在1片FPGA器件上實(shí)現(xiàn)信號源的信號產(chǎn)生和控制。將DDS信號源設(shè)計(jì)嵌入到FPGA器件所構(gòu)成的系統(tǒng)中,其系統(tǒng)成本不高,但可實(shí)現(xiàn)更加復(fù)雜的功能。

1 DDS原理

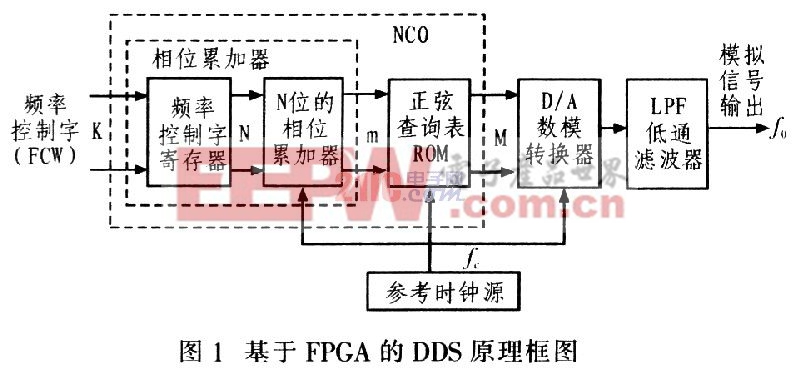

DDS基本結(jié)構(gòu)原理如圖1所示,其中數(shù)控振蕩器(NCO)為FPGA實(shí)現(xiàn)部分。其工作原理是:在參考時鐘的作用下,相位累加器按照預(yù)先設(shè)置好的頻率控制字進(jìn)行線性累加,其輸出作為波形查找表的地址,通過尋址輸出相應(yīng)的波形幅度碼,再由數(shù)模轉(zhuǎn)換器將這些數(shù)字碼變換為模擬電壓/電流輸出,最后經(jīng)低通濾波器平滑輸出波形。假設(shè)要輸出的頻率是同定的,那么相位增量就是一個常數(shù),在每個時鐘周期,相位累加器的數(shù)值就按照這個相位增量累加一次,相位增量的大小由頻率控制字決定。如果相位增量增大,則相位累加器的增加就比較快,輸出的頻率就比較高。

假定一個頻率為fc的載波,其時域表達(dá)式為:

則由式(1)、式(2)看出:C(t)是關(guān)于相位的一個周期函數(shù),如果記下一個周期內(nèi)每個相位對應(yīng)的幅度值,那么對于任意頻率的載波,在任意時刻,只要已知載波的相位φ(t),就可通過查表得到C(t)。

評論