基于FPGA視頻圖像的Canny算法加速器的設計

4 系統驗證和結果分析

為了能清楚直觀地驗證加速的加速效果,本文在系統平臺上對相同的圖像分別用加速/未加速的系統做處理,記錄相應時間并比較。

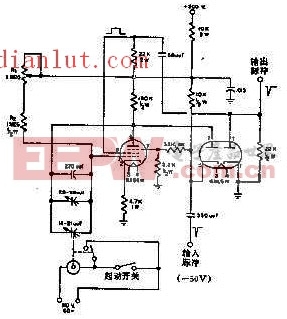

本文采用的驗證系統平臺以Altera公司CycloneⅡ系列中的EP2C20F484C8芯片為核心搭建而成,如圖4所示。在驗證系統設計中實現一個串口用來和PC機中的上位機通信,把處理完后的數據經過串口傳輸給上位機。數據在串口的傳輸過程中的延遲時間是固定的,故從上位機接收到第一個數據到最后一個數據的時間差即為一幀圖像處理所花費的時間。本文引用地址:http://www.czjhyjcfj.com/article/190119.htm

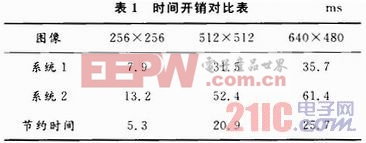

本文選取了不同大小的3幅圖片做實驗驗證,系統時鐘頻率為100 MHz。其處理時間結果如表1所示,系統1為有加速功能的系統,系統2為未經加速的系統。

由表1可見,經過加速改進后的系統在處理時間上得到了很大的節約,隨圖像尺寸變大,總的節約時間顯然是增加的;且經計算知:當尺寸變4倍(表1第2列256圖與第3列512圖),節約時間大約增加3.9倍;640×480圖比512×512圖尺寸大1.17倍,節約時間是1.23倍,實際結果與理論計算相吻合。隨著圖像尺寸的增加,節約時間亦按比例增加,因此該加速功能在處理大容量高速的圖像時具有更大的優勢和廣闊的應用前景。

圖5為一幅在FPGA中經過加速器系統處理后使用Matlab呈現的邊緣圖像。該算法處理的圖像結果基本得到所有的邊緣信息,完全能滿足應用需求。

5 結論

本文提出并實現了一種基于FPGA的加速Canny算法邊緣檢測系統。該系統充分發揮和利用FPGA的優良并行處理能力及流水線技術,從而實現功能加速。

在加速過程中通過狀態機的控制作用能使模板的運算處理和數據的讀/寫操作得以同時進行,一定程度上節約了因大量的讀/寫數據操作而占用的時間。此系統充分利用了FPGA中的硬件資源,大大提高了系統算法的運算效率,且設計結構較為靈活。最終通過邊緣檢測實驗,驗證了設計的正確性。

fpga相關文章:fpga是什么

評論