基于FPGA視頻圖像的Canny算法加速器的設計

2.1 加速器設計實現

本文使用了一種能運用于高斯平滑濾波和梯度計算的加速器的數據路徑結構。由于這兩種計算過程均采用相同大小的方形移動窗口,故其加速設計具有極大的相似性。對此,這里選取3×3的Sobel模塊來解釋說明。本文引用地址:http://www.czjhyjcfj.com/article/190119.htm

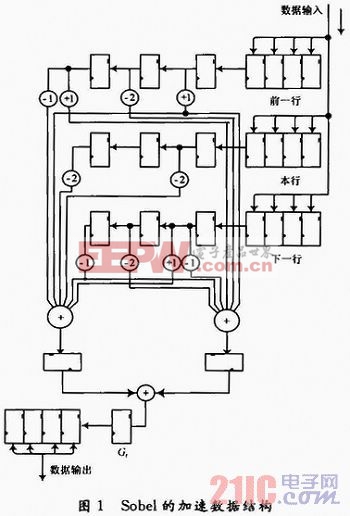

Sobel的加速數據結構如圖1所示。它是一個具有以下功能的流水線:先從原始的圖像中讀取像素值存入圖中右方的3組12寄存器中,數據流過中間的3×3的乘法器陣列,即像素值與模板值做乘法運算;然后向下流過加法器,在加法器中完成和運算,至此實現了像素值與模板的卷積運算,之后到達Ex和Ey寄存器,通過絕對值電路和加法器(實現式(4))到達寄存器,最終流入最下面的寄存器。圖中負號表示取反,數值1和2表示右移的位數。

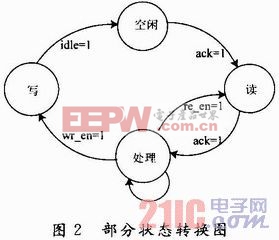

為使得加速器能夠有序地按照確定的步驟進行,本文使用了有限狀態機。如圖2所示為加速器的簡單狀態轉換圖。在加速器的執行過程中,當檢測到3組寄存器中的數據為空時,讀信號使能re_en置1,自動讀入新的3組數據;且在下方寄存器存儲滿時,寫信號使能wr_en置1,數據被提取進行寫操作。

在加速器的執行過程中,像素每4個為一組進行讀寫,這樣在高速處理過程中大大縮減了對相同像素點的多次重復讀取而浪費的時間;同時,在處理過程中不需要在處理每個像素點時都對其鄰域的8個像素點更新,這樣節省了大量的讀取時間;并且由于FPGA的并行特性,像素的讀、移位及寫操作和乘法器的運算是同時進行的,使得處理速度有一定的提升。

fpga相關文章:fpga是什么

評論