使用 PlanAhead Design 工具提高設計性能

一個 Virtex-4 布局規劃示例

PlanAhead 設計工具可允許您輕松地導入布局和時序結果。通過該信息,您可以查看和排序時序報告中的關鍵路徑,并使用原理圖或器件視圖對路徑進行可視化顯示。一旦確定故障路徑,您可以高亮顯示布局規劃中的所有路徑實例,以確定原理圖視圖中的所有路徑實例。

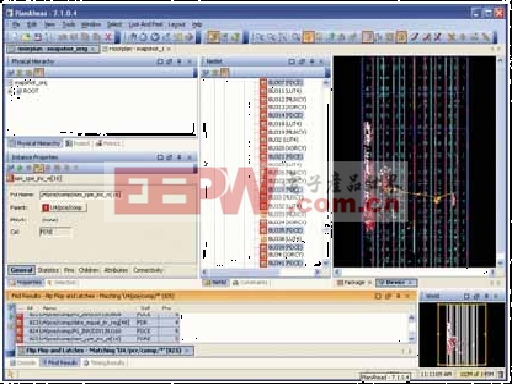

圖 3 顯示了一個針對 Virtex-4 FX140 器件的設計的布局規劃。在顯示中,我們高亮顯示了一條特定路徑上未能滿足時序要求的觸發器。由于它們在器件中分布太廣,設計實現產生了無法接受的長延遲。由于在 Virtex-4 FPGA 中存在大量的時序域,因此這是一種普遍情況。

圖 3:初始 Virtex-4 FPGA 布局規劃,高亮顯示開始未滿足時序的路徑

通過選擇這些觸發器中的每個觸發器,并將它們限制到單個 Pblock 中,您可以調節和優化該 Pblock的尺寸和位置,從而縮短關鍵路徑的延遲,如圖 4 所示。必要時,您甚至可以創建嵌套 Pblock,從而創建一種子/主層次來進一步約束子模塊,以獲得額外的性能提升。根據捕獲邏輯的資源需求,您可以將關鍵邏輯鎖定位置,以實現對必要資源的最佳訪問。

圖 4:在對與該路徑相關的所有基元進行約束后,您可以對 Pblock 進行優化,以使該路徑達到所需的時序要求。

結論

您可下載 PlanAhead 軟件的免費評估版本。該 30 天評估版使您可完全獲得所有 PlanAhead 特性和功能性。該站點還允許您查看產品演示,下載白皮書,或只是了解更多信息。賽靈思還提供 PlanAhead QuickSTart!,可在項目的最關鍵階段提供特別的服務支持。通過該服務,賽靈思將派遣一名 QuickStart! 工程師到您的現場進行為期一周的輔助,他將培訓和幫助您的團隊按時完成項目和如何充分利用您所選擇的賽靈思器件。

這一高度個性化服務使您能制定最能滿足您的設計團隊需要的培訓計劃。通過確保團隊擁有所需的技能,它將有助于避免項目拖延。它還有助于您保持一個更有效率且熱情高漲的團隊。

評論